This article was originally published on amigaportal.cz in April 2024. In this text are minor corrections.

Today, at the beginning of 2024, we are experiencing an unusual situation in the AmigaNG world. We have two entry-level computers to choose from: in 2023, ACube introduced a new version of Sam460 - Sam460LE, and this year, after a long journey full of obstacles, AAA technology introduced the A1222 Plus.

The coincidence of two computers of the same category is something quite unusual in the AmigaNG world, so it is often discussed which one is which and which one is better.

In this article we will look at how it really is from the theoretical side. And, what is unusual for me, the article does not contain a single chart with benchmarks. Of course you won't miss those after all, we'll just talk about them sometime later when I get more familiar with the new machines.

1. Chapter One - Motherboards

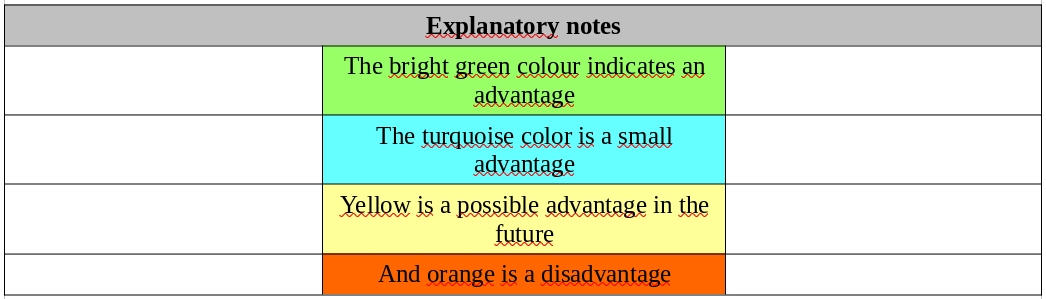

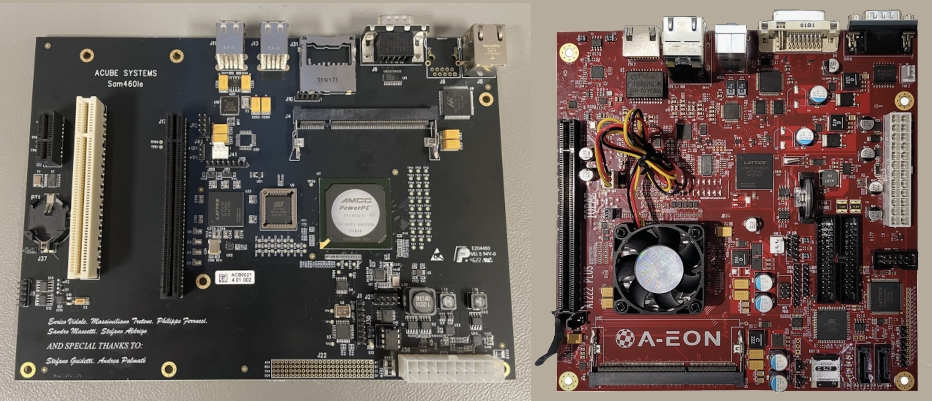

When comparing the motherboards, one difference is apparent at a glance: the Sam460LE is Micro-ATX and the A1222+ Mini-ITX.

Sam460LE has the advantage of easier future expansion. Even if all PCIe slots are occupied in the normal configuration, we can fit a 1x1 -> 4x1 PCIe switch if needed. We can also install MorphOS on the Sam460, which is great bonus.

The A1222+ is smaller, has a SATA II controller and 8 GB of DDR3 ( memory used by Linux and some AmigaOS applications ).

The A1222+ has another advantage not mentioned in the table, namely the NGFS filesystem. It is more modern and faster than SFS/02 and so far only the A1222+ and X5000 use it.

Other advantages such as two Ethernet ports and a much more powerful coprocessor are only theoretical, because AmigaOS cannot use them yet.

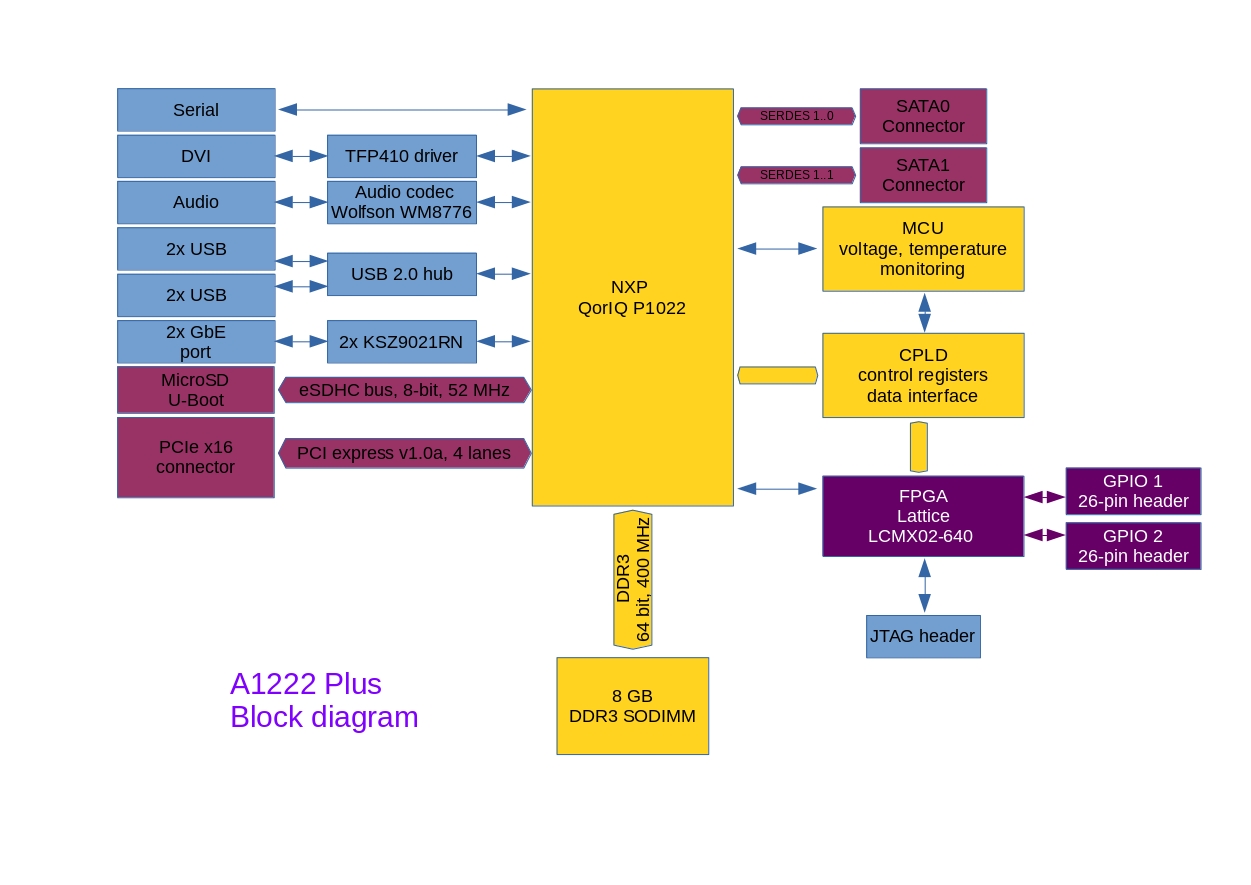

1.1 Computer block diagrams

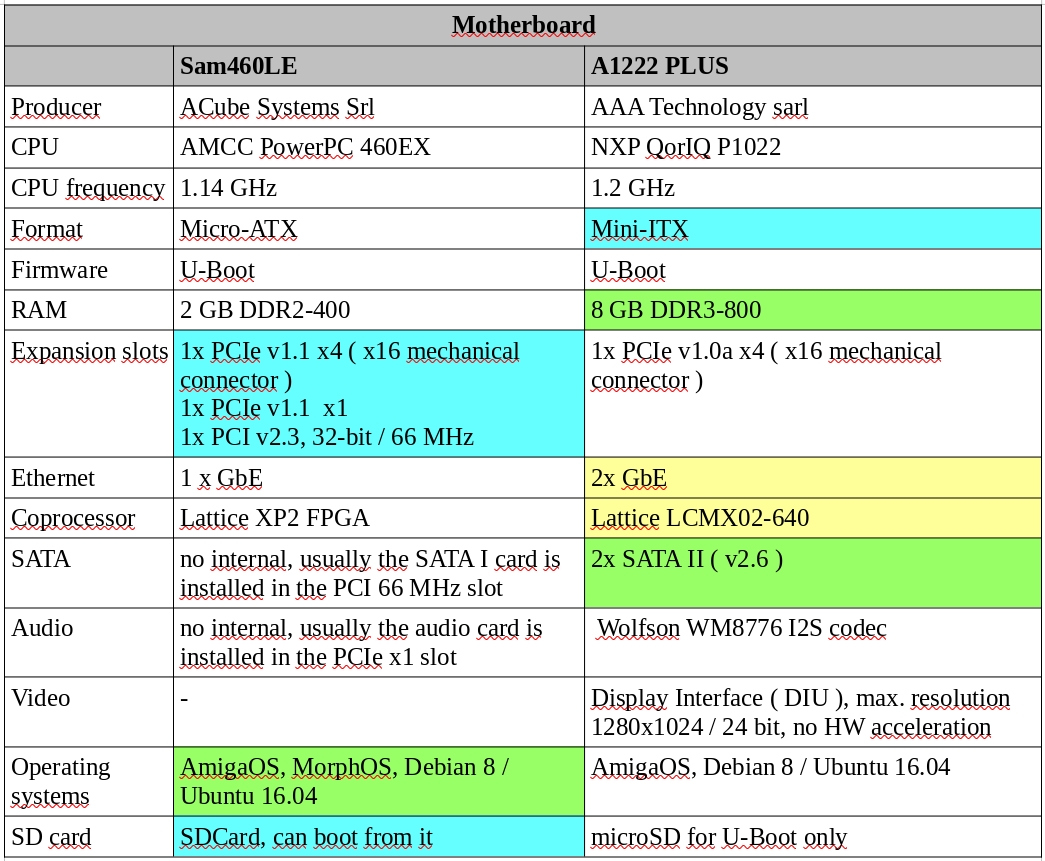

The original Sam460ex also included a SATA II connector and an audio/video chip with 2D acceleration. The cr/LE versions no longer include them, they were not used in practice.

The Lattice coprocessor is connected to the local bus of the processor ( EBC, OPB, see below ).

The SD card is connected as a USB device and can hold kernel modules or the entire operating system and boot is possible directly from it.

The LCD interface of the A1222+ is part of the CPU and is without hardware acceleration. It is therefore not suitable for a desktop system. It could be used for a server - by using the LCD interface wee can free up a PCIe x4 slot.

The Lattice coprocessor is connected via the main CPLD, which, in addition to communicating with the coprocessor, controls the speed of the fans. The MCU then monitors the voltage and temperature of the CPU.

The microSD is connected to the eSDHC controller of the processor. The card only has firmware ( U-Boot ) and is not accessible from the system. Theoretically, with a suitable driver it could be accessible, the MicroSD card contains space for MBR partition map, but it would be unreasonable. We could easily corrupt the firmware by mistake.

At first glance, both computers are quite similar. Since both processors are SOCs ( System On Chip ) and therefore the most important part of the computers is inside them, they deserve a closer look.

Since a cursory glance at the parameters is not enough, let's dig deeper to see what lies beneath the surface. Inside the CPU.

2. Chapter Two - Processors

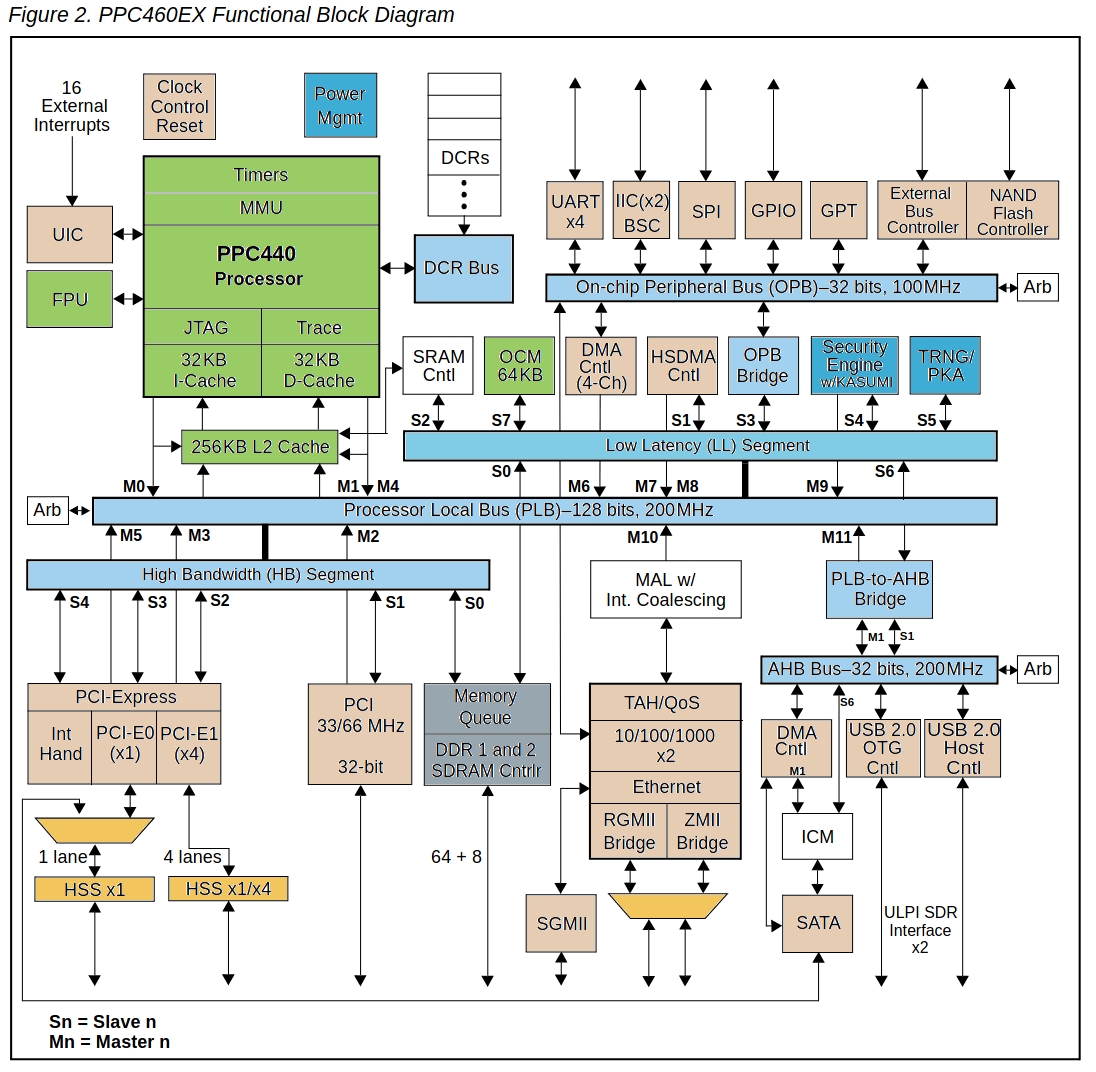

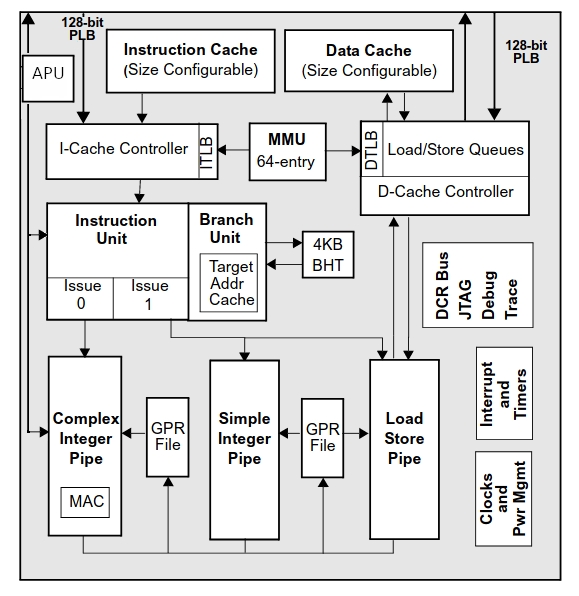

2.1 AMCC PowerPC 460EX processor block diagram

This processor diagram is a bit confusing at first glance because it is quite detailed. So let's explain it a bit.

First of all, the FPU ( Floating point unit ) is not part of the core as is common with Powerpc processors. The FPU is connected to the CPU as an APU ( Auxiliary Processor Unit ), shares its pipelines and has a standard set of 32x 64-bit FPR registers. Therefore, we will consider it as part of the core from our point of view.

The processor has four internal buses:

Processor Local Bus (PLB): to which two segments are connected:

- High Bandwidth (HB) segment that interconnects memory controllers, PCIe and PCI as well as the AHB bridge;

- Low Latency ( LL ) segment, connects the On Chip memory, two DMA controllers and the OPB bridge.

On-chip Peripheral Bus (OPB): it connects slower peripherals and the External Bus Controller (EBC) is also connected here, to which the Lattice XP2 coprocessor is connected in Sam's case.

Advanced High-performance Bus (AHB): connects USB and, in the case of Sam460ex, an internal SATA II controller with its own DMA controller.

Device Control Register bus (DCR): internal connection for status and control information from individual CPU components.

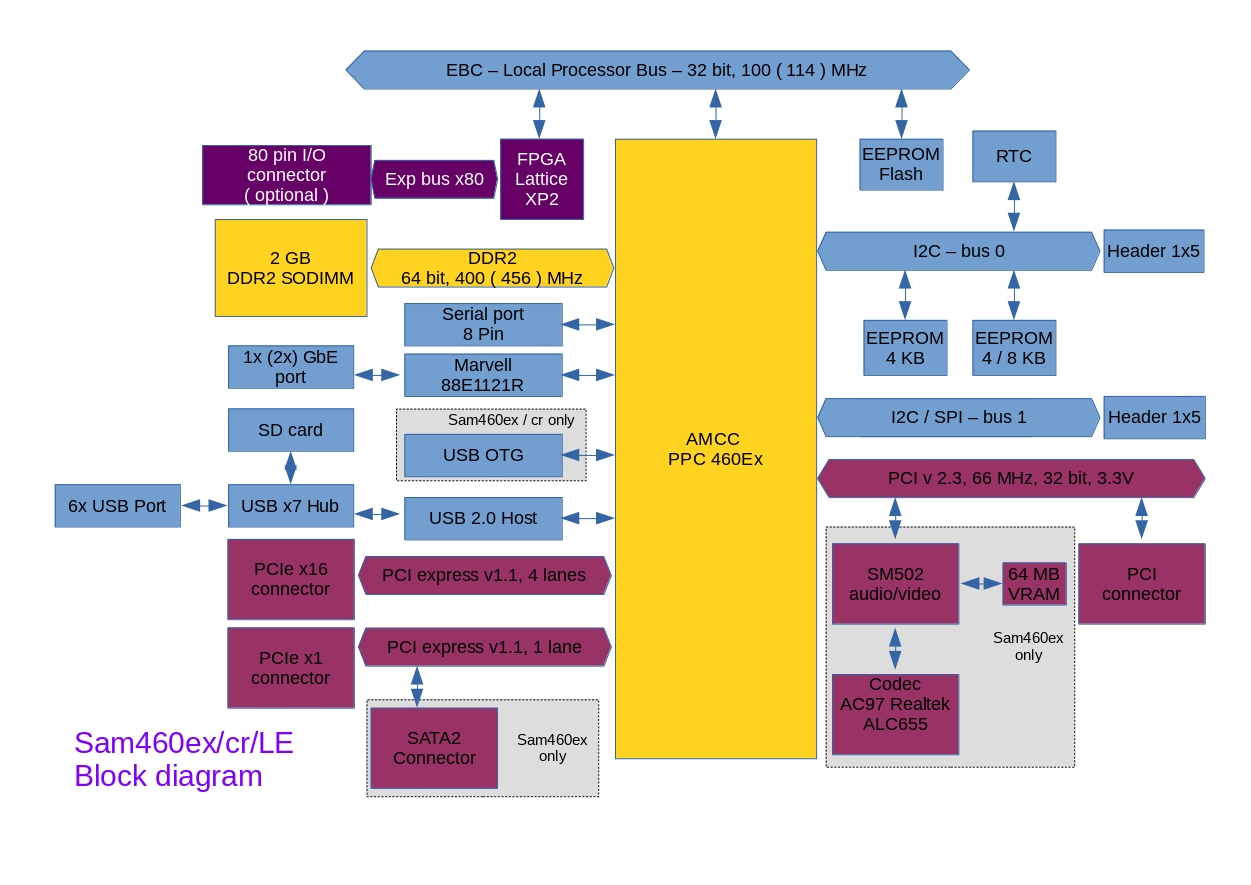

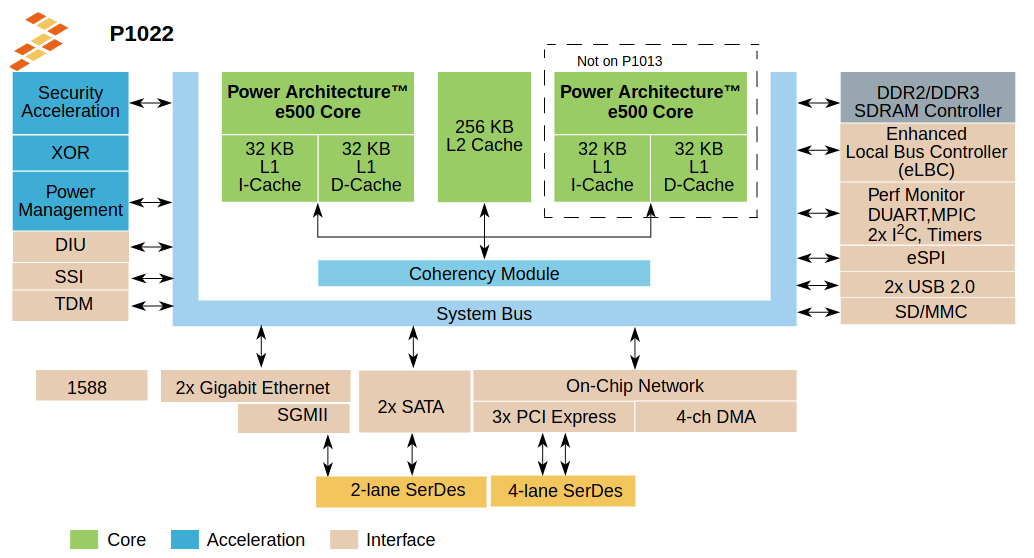

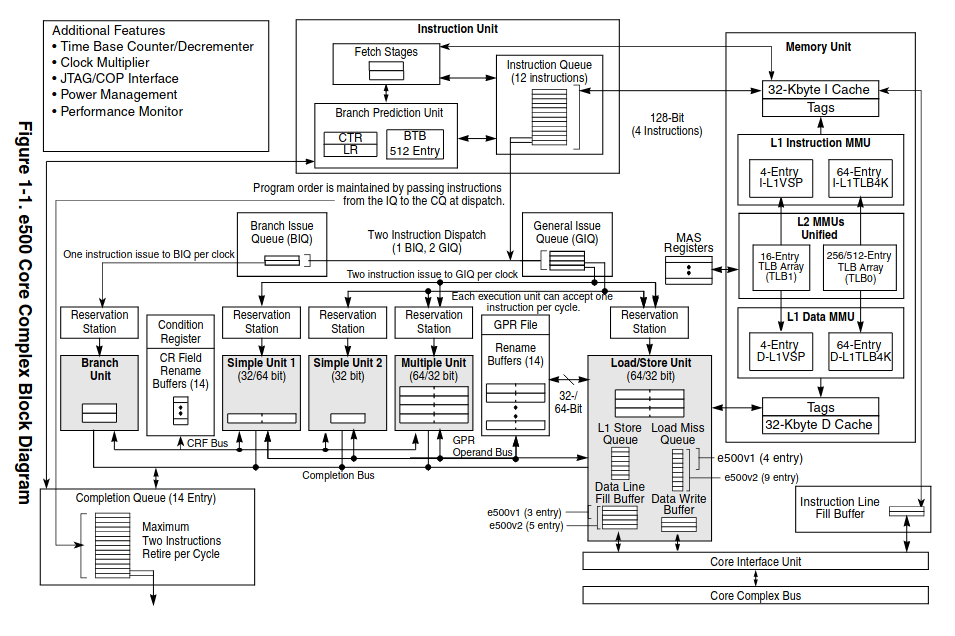

2.2 NXP QorIQ P1022 Processor Block Diagram

This diagram is less detailed, so just briefly:

The two processor cores with a common L2 cache are connected via the Coherency Module to the System Bus. The Lattice LCMX02-640 coprocessor is then connected via the Enhanced Local Bus Controller ( eLBC). The other connections are obvious enough.

Apart from schematics, we will be mainly interested in the differences in processor characteristics:

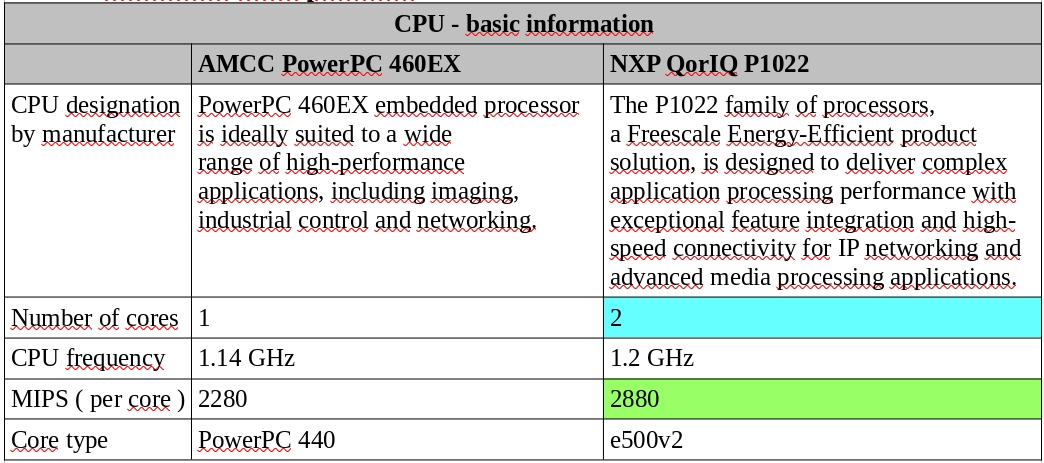

2.3 Basic information about processors

Both processors are similar in purpose and as the description suggests, both have good IP and data stream processing characteristics ( obviously relative to their time of creation ).

The frequency of the processors is similar, but the P1022 has a higher raw performance per core at a given frequency and is also dual-core. While this will only be used in Linux today, a new ExecSG is in the works that will use both cores in AmigaOS as well.

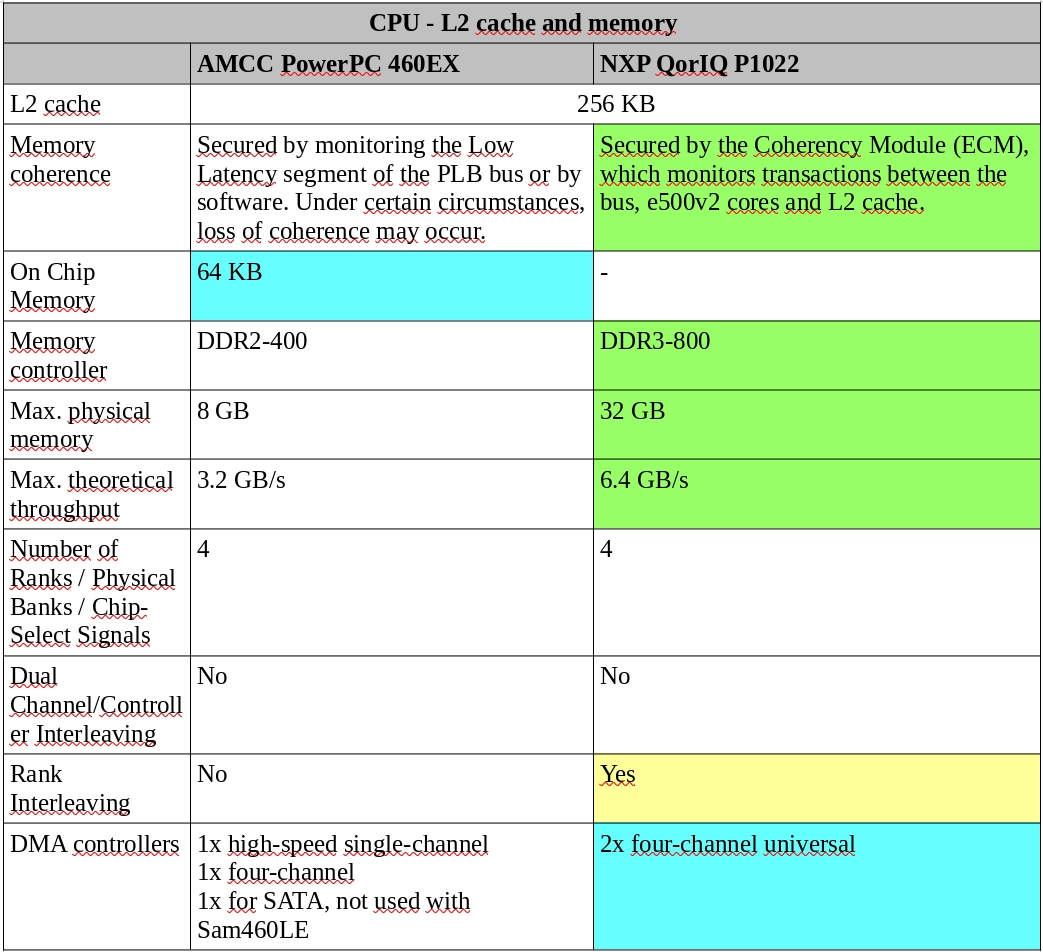

2.4 Processor memory subsystem

Both processors have 256 KB of L2 cache. However, memory coherency is not guaranteed at all times with the 460ex processor. This leads, for example, to device drivers sometimes having to clear the L2 cache and Radeon drivers not having a working GART. The P1022 will therefore be slightly faster.

However, the 460ex processor also has an additional 64 KB of fast On Chip Memory in addition to L2 - it is connected via a 128-bit bus and is used for packet data processed by the Security Engine and Ethernet modules, among others.

The DDR controller in the P1022 is a generation more advanced. It can address more physical memory, it is faster and although it does not have Dual Channel, it has Rank Interleaving, which speeds up operations by about 10%. Unfortunately, the A1222+ firmware can't initialize Rank Interleaving yet, but since U-Boot is still evolving and the X5000 can already do it, we may see it in the future.

Since both computers have only one DDR connector on the motherboard, we are limited to the maximum size of the SO-DIMM modules.

So you can fit up to 8 GB with a DDR3 module ( with 2R or 4R geometry ) into the A1222. I have successfully tested the 8 GB module ( 2R8 ) Kingston Fury ( KF318LS11IB/8 ).

Sam460LE can have up to 4 GB theoretically with a DDR2 module ( 2R or 4R ). I haven't tried that, I don't have a 4 GB module available. For the Sam, it is indeed listed as maximum 2 GB memory, but since the U-Boot is also still under development here, could the 4 GB support be added ( if not already there ).

For the 460ex processor, the single channel DMA controller is used for transfers from fast peripherals ( it can do memory<->memory and memory<->peripherals, not directly peripherals<->peripherals ) and the four channel controller is only for devices on the On-chip Peripheral Bus.

The P1022 has two universal four-channel DMA controllers for any transfers.

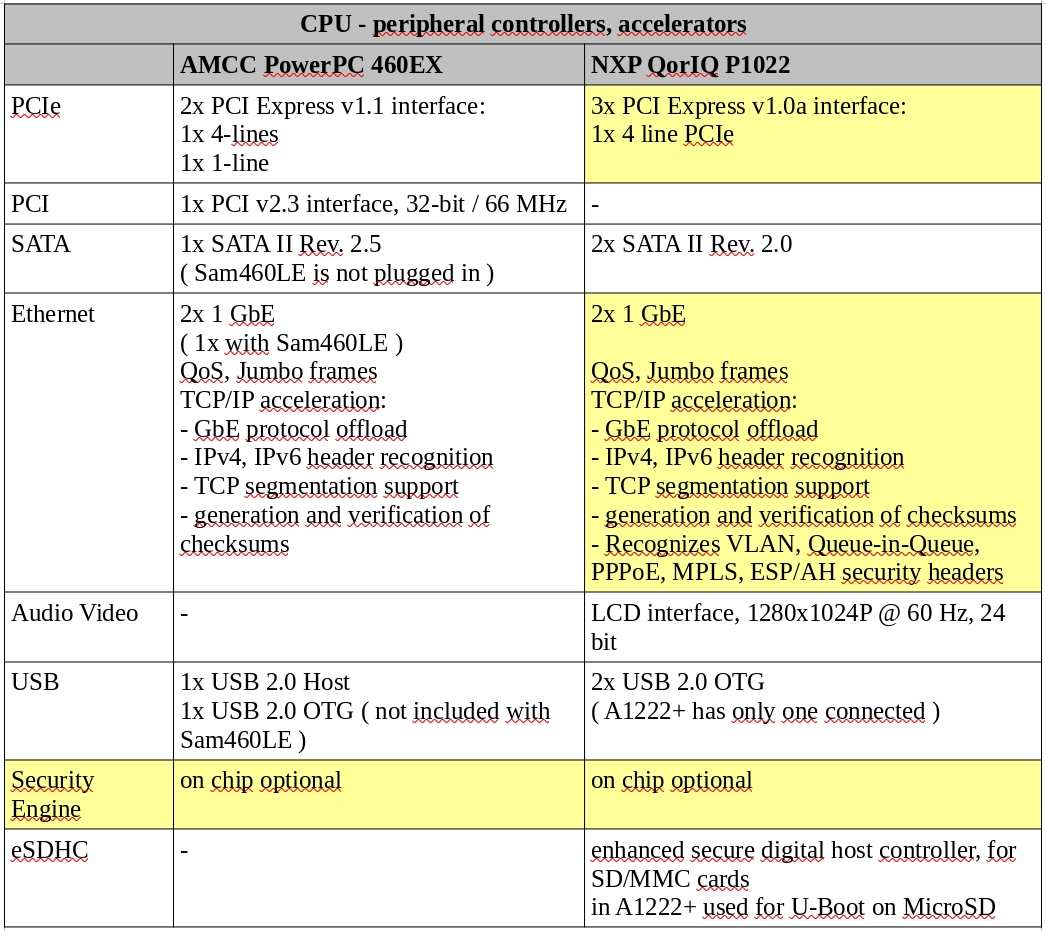

2.5 Processor peripheral controllers

The P1022 processor has a total of 6 SERDES configurable lines, one channel with 4 lines, the second channel with 2 lines. The configuration is defined in the firmware.

The physical wiring in the A1222+ is as follows: 4x PCIe, 2x SATA. If the U-Boot allows it in the future, a so-called bifurcation ( splitting the PCIe bus without a switch ) can be done on the PCIe port. The processor can have up to three PCIe interfaces, so there are realistic combinations:

PCIe x4 ( default ), PCIe x2 + x2, PCIe x2 + x1+ x1. In this way, it would be possible to expand the A1222+ with additional devices in the future, at the cost of limiting the data flow to the graphics card, of course.

The 460ex processor shares a single SERDES ( marked as HSS on the ppc460ex schematic ) for both PCIe x1 and SATA. On the Sam460LE, PCIe x1 is hardwired.

Both CPUs have TCP hardware acceleration, e500v2 has advanced VLAN, QiQ, MPLS ... Of course, in the AmigaOS TCP stack ( so far ) unused.

Both processors can also have a Security Engine ( SEC ) - hardware acceleration of IPSEC, SSL/TLS and many other crypto + hash algorithms. But this option is optional when ordering the CPU, so I assume the SEC versions of the CPU are not in either the Sam460LE or the A1222+ ( and I don't want to take the fans off just to look at the code ).

As already a big hardcore it would be possible to replace the processors with versions with this engine. And then ( er,... ) write a driver for AmigaOS ( linux could do it ? ). For a reward we would get for example a substantial speeding up of the internet. And that wouldn't hurt in this day and age of encryption.

When comparing the processors, it is clear that the P1022 has more advantages. But we haven't found out the main thing yet.

In the next chapter, we'll go even deeper, into the bowels of the processor all the way to the core. And see if we can find something unexpectedly nice there, too.

3. Chapter Three - Processor Cores

3.1 differences in the cores

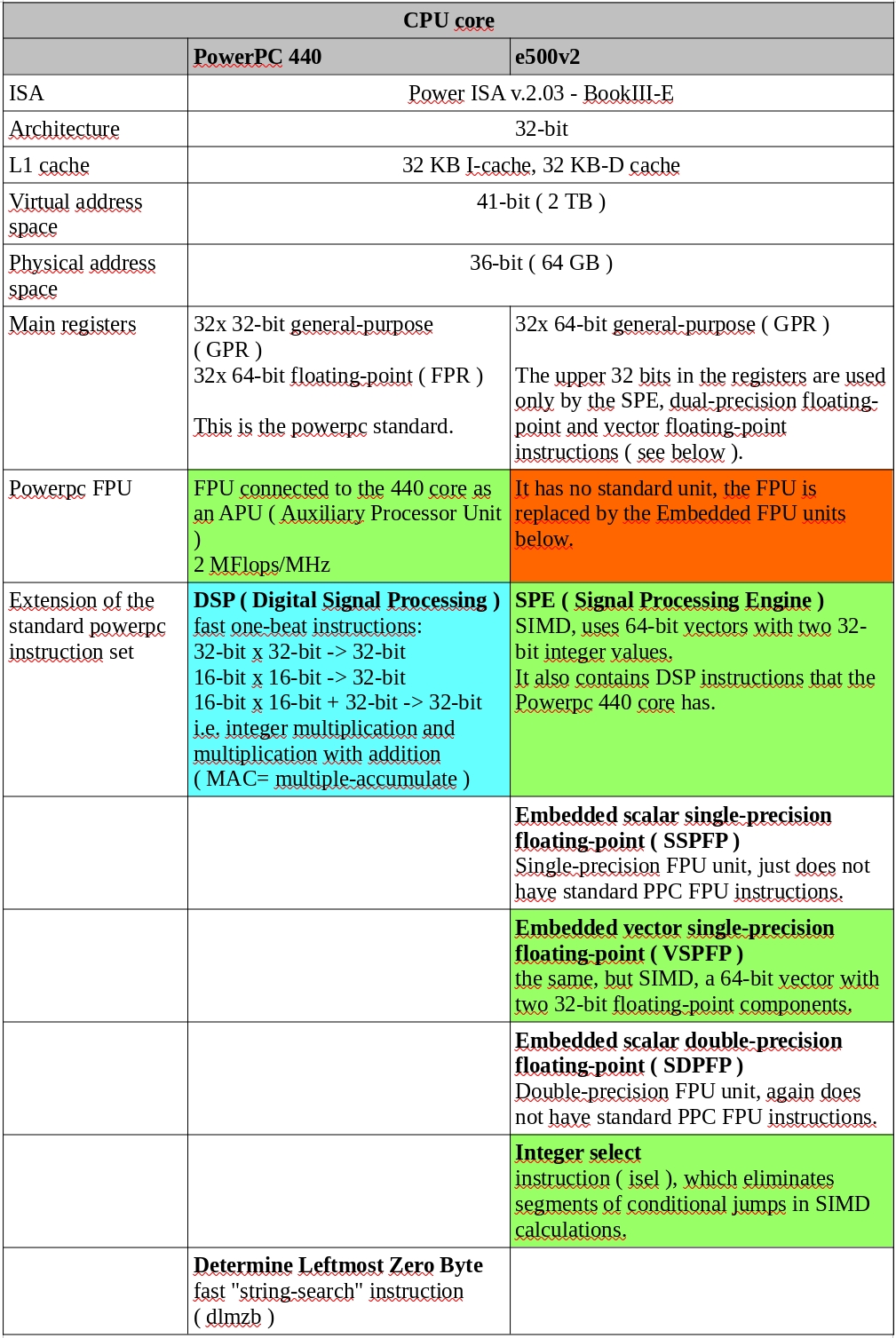

Both cores are 32-bit and have the same ISA. They differ in register sets, FPUs and SIMD units.

Let's take another look at the core schematics. This time it will be a more detailed diagram of the e500v2.

3.2 PowerPC 440 block diagram

The PPC440 core has three execution pipelines ( units ), processes up to two instructions per clock and executes and terminates them out-of-order. Details on how instructions are processed can be found here: https://www.amigaportal.cz/node/155095 (CZ).

The FPU, although not directly in the core, behaves as part of the core. It is connected to the APU interface and directly shares the core pipelines ( Complex Integer Pipe ).

Only the 32-bit GPR registers are in the core. The 64-bit FPR registers are again contained in an external FPU and appear to be part of the core from an ABI ( Application Binary Interface ) perspective.

However, what is extra in the core compared to the classic Powerpc processors is the DSP/MAC extension ( APU ). It is contained directly in the Complex Integer Pipe. The execution time of these instructions is one clock, so it is suitable for processing streams of similar data ( streams ).

3.3 block diagram of e500v2

This core has five execution units ( the grey ones in the diagram ), processes instructions out-of-order ( up to two instructions + one jump per clock ) and terminates them in-order.

This core also has only GPR registers, but this time extended to 64-bit. It does not contain FPR registers at all.

There is no standard powerpc FPU, it is replaced by these units:

Embedded scalar single-precision floating-point

Embedded scalar double-precision floating-point

However, these units have a different instruction set than the powerpc FPU and use 64-bit GPR instead of FPR.

But the most interesting thing about this processor is the SIMD units ( Simple Instruction Multiple Data ). It contains two of them:

SPE ( Signal Processing Engine ) is a vector unit that processes integer vectors with two 32-bit or four 16-bit values.

Embedded vector single-precision floating-point APU is a vector unit for vectors with two floating-point values.

SPE instructions are executed directly in 64-bit Simple and Multiple Units ( Unit ) and again use 64-bit GPR.

In comparison, Altivec / VMX handles double-length ( 128-bit ) vectors and has an extra Permutation Unit.

Here in the cores is finally the answer to all discussions about whether the A1222+ ( or its CPU ) is powerful enough or suitable for AmigaOS.

4. the answer to Ultimate Question of Life, the Universe, Everything and Entry-level AmigaNG in general

The basic question is: Is the A1222+ more powerful than the Sam460LE ? Unlike mice, we don't have to wait seven million years for an answer. The answer may not be 42, but it is still very simple:

YES and NO

NO: because the normal powerpc code containing FPU instructions must be handled by interrupt and emulated in the P1022 processor. There are two FPU instruction emulators available in AmigaOS:

- LTE ( load time emulator ): This is the default. This is a JiT compiler with a relatively high speed - in my tests it was only 1.2x to 4.5x slower than the original FPU. So it's beautiful. But it has a downside: like any JiT compiler, it doesn't have 100% compatibility with the original code. Some applications don't work with it.

- Standard interpreter emulator: use it when LTE is not working ( set in Prefs:Compatibility ). It is already significantly slower ( 20x to 70x ) than the classic FPU, but it is 100% compatible. It's actually the same as when we have the MC68LC060 processor and softieee.library in a classic Amiga. It's not fast, but it works.

And this is the very reason why apps like Blender or some 3D FPS games will be slow on the A1222+ until someone translates them natively for the A1222+.

YES: because the e500v2 core contains embedded FPUs, so all software can be compiled to use these units and the result is just as fast. Actually a bit faster, because the P1022 has slightly higher raw performance than the AMCC 460ex.

Yes, and by a lot: because the e500v2 includes two SIMD extensions. They're not nearly as powerful as the aforementioned AltiVec/VMX, which incidentally completely outperformed Intel's SSE and SSE2 at the time, but they're interesting nonetheless.

The "Integer select" instruction serves as a supplement for vector calculations, which eliminates conditional jumps in SIMD code. See for example here, paragraph 2.5: http://ftp.cvut.cz/kernel/people/geoff/cell/ps3-linux-docs/CellProgrammingTutorial/BasicsOfSIMDProgramming.html

If we have application code written directly for SIMD processing, it will be significantly faster than regular powerpc code.

From a developer's point of view, using Embedded FPU and SPE is a bit more complicated - eFPU has a different set of registers than the standard powerpc, so calling floating-point functions from standard libraries is a bit more difficult. Not to mention that SPE instructions require 8-byte stack alignment. While this should be obvious according to the Powerpc ABI standard, not all applications follow this.

More details e.g. here: https://keasigmadelta.com/blog/taborizing-drivers-and-libraries-a-k-a-optimizing-for-the-e500-spe/

But even Sam can do better than that: All Sam 460s and all Sam 440s are capable of fast single-stroke DSP ( MAC ) instructions (see above). Yes all of them, because their processors have the same core, the Powerpc 440. If we have a task with high time complexity that depends on integer multiplication and addition ( for example, most cryptographic and hashing operations as well as some codecs ), Sam can also be faster than classical powerpc code. SPE in P1022 or Altivec in G4 also have such instructions, but for example the G3 processor does not. I mean, it can't do so fast in one clock.

In addition, using DSP instructions with Sam has a big advantage - it uses the standard ABI, so there is no need to make any changes to the rest of the code like with SPE. So in general, I would encourage developers to take advantage of this option for Sam4x0 computers.

Sam also contains a "dlmzb" instruction. This is used to quickly search the string in exactly the way its name implies - it searches for the first non-zero byte. For what tasks it could be used in a desktop operating system, however, I have no idea.

5. The end and what next

So now we know what advantages both computers and their processors have. They outperform their first generation predecessors with the ability to use modern PCIe cards and newer controllers.

Of course, they do not reach the performance of their bigger sisters AmigaOne X1000 and X5000, they are only entry-level systems.

But both have something extra over the desktop G3 processors. They can use Multiply-accumulate instructions and the A1222+ also has two SIMD units. It's a shame to let these capabilities lie fallow, it would certainly be worth recompiling some of the time-consuming algorithms to take advantage of the SPE and MAC.

So next time we can start testing real hardware. It will go quickly, I have four similar helpers, already very experienced in computer work.

Important addendum 2025:

The experienced helpers in the last picture are now five - three cats and two Jack Russels. The eldest cat is so skilled that she ( in an effort to help me test the hardware ) knocked my A1222+ to the floor and smashed the video card.

Special thanks to:

ACube and AAA Technology for new beautiful toys

Images used:

Logos: shop.acube-systems.biz, a1222plus.com, modified

Motherboards: shop.acube-systems.biz, amigakit.fr, modified

Glacier: flickr.com

Deep Sea octopus: g.cz

CPU schematics: 460EX PowerPC 460EX Embedded Processor Datasheet and P1022 QorIQ Integrated Processor Hardware Specifications, modified

PPC440x5 CPU Core User's Manual and PowerPC e500 Core Family Reference Manual, modified

Kitty: the-great-beyond.blogspot.com