# PPC440EP

**Data Sheet**

## PowerPC 440EP Embedded Processor

## **Features**

- PowerPC<sup>®</sup> 440 processor core operating up to 667 MHz with 32 KB I-cache and D-cache with parity checking.

- Selectable processor:bus clock ratios of N:1, N:2.

- Floating Point Unit with single- and doubleprecision and single-cycle throughput.

- Dual bridged Processor Local Buses (PLBs) with 64- and 128-bit widths.

- Double Data Rate (DDR) Synchronous DRAM (SDRAM) interface operating up to 133MHz with ECC.

- DMA support for external peripherals, internal UART and memory.

- PCI V2.2 interface (3.3V only). Thirty-two bits at up to 66MHz.

- Programmable interrupt controller supports interrupts from a variety of sources.

- Programmable General Purpose Timers (GPT).

- Two Ethernet 10/100Mbps half- or full-duplex interfaces. Operational modes supported are MII, RMII, and SMII with packet reject.

- Up to four serial ports (16550 compatible UART).

- Two USB ports. One USB 1.1 Host interface with on-chip PHY. One USB 2.0 Device interface, with dedicated DMA, configured as a 1.1 on-chip PHY or a 2.0 UTMI.

- External peripheral bus (16-bit data) for up to six devices with external mastering.

- Two IIC interfaces (one with boot parameter read capability).

- NAND Flash interface.

- · SPI interface.

- General Purpose I/O (GPIO) interface.

- JTAG interface for board level testing.

- Boot from PCI memory, NOR Flash on the external peripheral bus, or NAND Flash on the NAND Flash interface.

- · Available in RoHS compliant lead-free package.

### **Description**

Designed specifically to address high-end embedded applications, the PowerPC 440EP (PPC440EP) provides a high-performance, low-power solution that interfaces to a wide range of peripherals and incorporates on-chip power management features.

This chip contains a high-performance RISC processor, a floating point unit, DDR SDRAM controller, PCI bus interface, control for external ROM and peripherals, DMA with scatter-gather support, Ethernet ports, serial ports, IIC interfaces, SPI interface, USB ports, NAND Flash interface, and general purpose I/O.

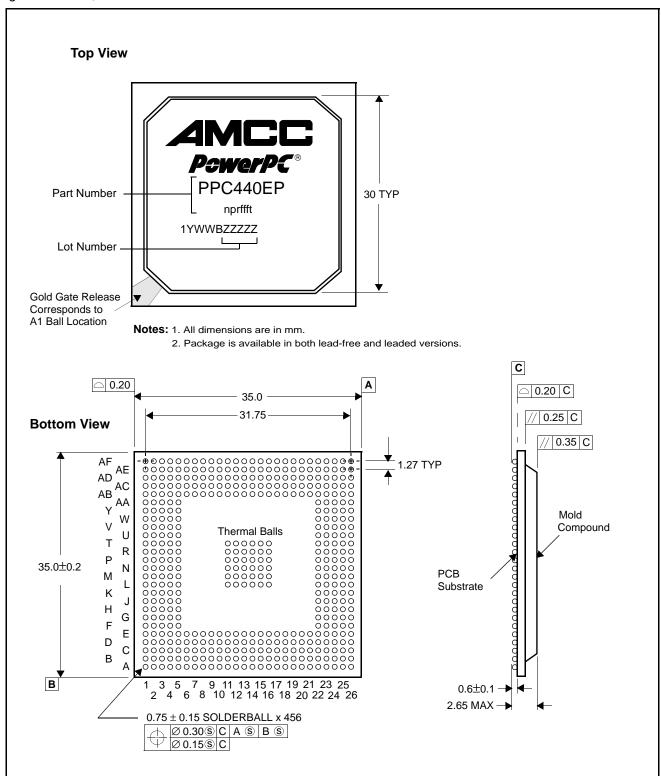

Technology: CMOS Cu-11, 0.13 µm.

Package: 35mm, 456-ball standard plastic ball grid array (E-PBGA), with and without lead (RoHS compliant).

Typical power (measured): Less than 3W at 533MHz, 2.5W at 400MHz.

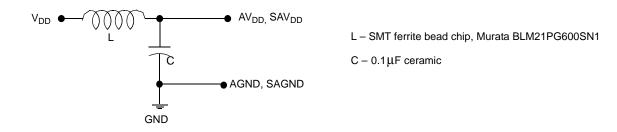

Supply voltages required: 3.3V, 2.5V, 1.5V.

### **Contents**

| Ordering and PVR Information             | 5  |

|------------------------------------------|----|

| Block Diagram                            | 6  |

| Address Maps                             | 7  |

| PPC440EP Features                        | 0  |

| PowerPC 440 Processor Core               | 0  |

| Floating Point Unit (FPU)                | 0  |

| Internal Buses                           | 1  |

| PCI Interface                            | 2  |

| DDR SDRAM Memory Controller              | 2  |

| External Peripheral Bus Controller (EBC) | 3  |

| Ethernet Controller Interface            | 3  |

| DMA to PLB3 Controller                   | 3  |

| DMA to PLB4 Controller                   | 4  |

| Serial Ports (UART)                      | 4  |

| IIC Bus Interface                        | 4  |

| Serial Peripheral Interface (SPI/SCP)    | 5  |

| Universal Serial Bus (USB)               | 5  |

| NAND Flash Controller                    | 5  |

| General Purpose Timers (GPT)             | 6  |

| General Purpose IO (GPIO) Controller     | 6  |

| Universal Interrupt Controller (UIC)     | 6  |

| JTAG 1                                   | 6  |

| Package Diagram                          | 7  |

| Assembly Recommendations                 | 8  |

| Signal Lists                             | 9  |

| Signal Descriptions                      | 0  |

| Device Characteristics 6                 | 31 |

| Clocking Specifications                  | 8  |

| I/O Specifications                       | '0 |

| DDR1 SDRAM I/O Specifications            | 7  |

| Boot Configuration                       | 36 |

| Revision Log                             | 37 |

## Revision 1.30 – June 21, 2012

## **PPC440EP Embedded Processor**

# Data Sheet

| Figures                                                 |

|---------------------------------------------------------|

| Figure 1. Order Part Number Key                         |

| Figure 2. PPC440EP Functional Block Diagram             |

| Figure 3. 35mm, 456-Ball E-PBGA                         |

| Figure 4. Overshoot Waveform                            |

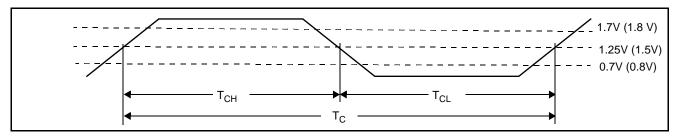

| Figure 5. Timing Waveform                               |

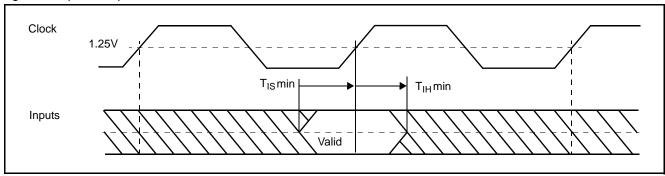

| Figure 6. Input Setup and Hold Waveform                 |

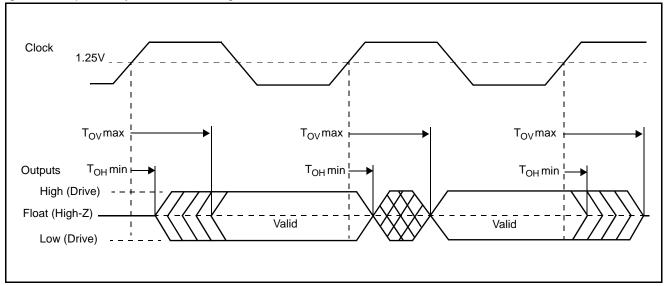

| Figure 7. Output Delay and Float Timing Waveform        |

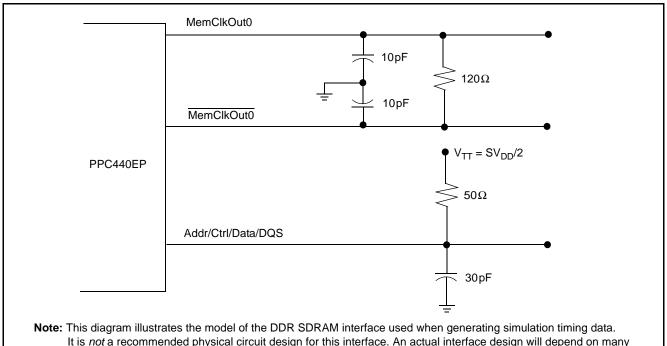

| Figure 8. DDR SDRAM Simulation Signal Termination Model |

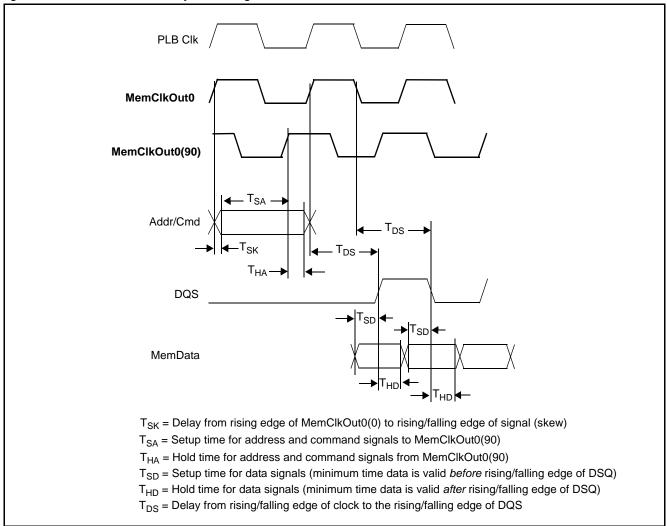

| Figure 9. DDR SDRAM Write Cycle Timing                  |

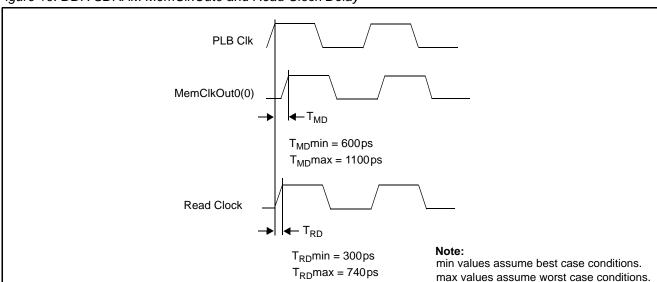

| Figure 10. DDR SDRAM MemClkOut0 and Read Clock Delay    |

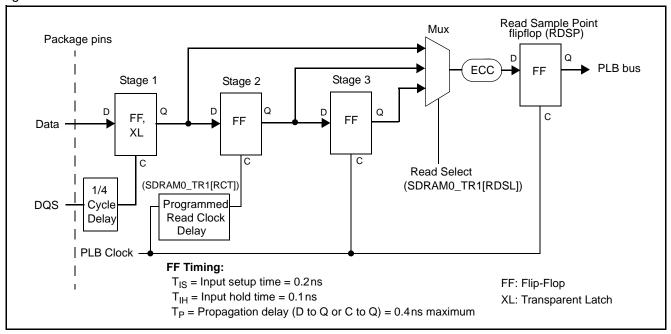

| Figure 11. DDR SDRAM Read Data Path                     |

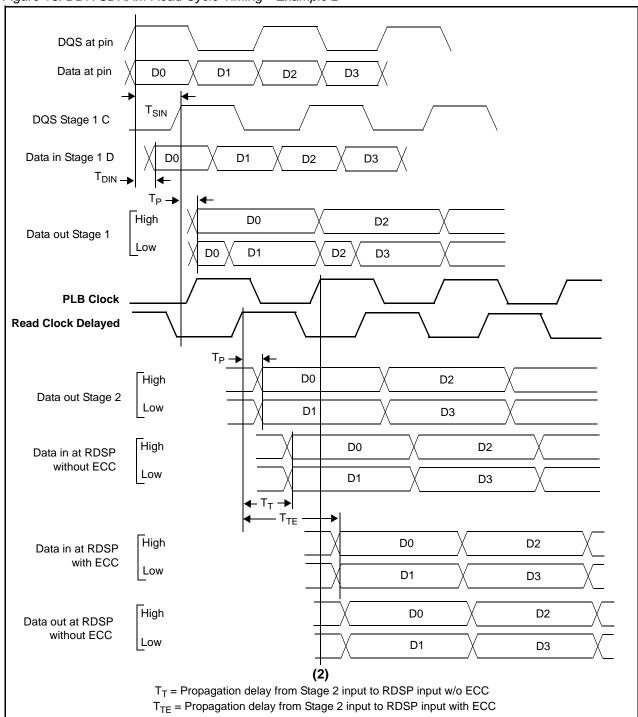

| Figure 12. DDR SDRAM Read Cycle Timing—Example 1        |

| Figure 13. DDR SDRAM Read Cycle Timing—Example 2        |

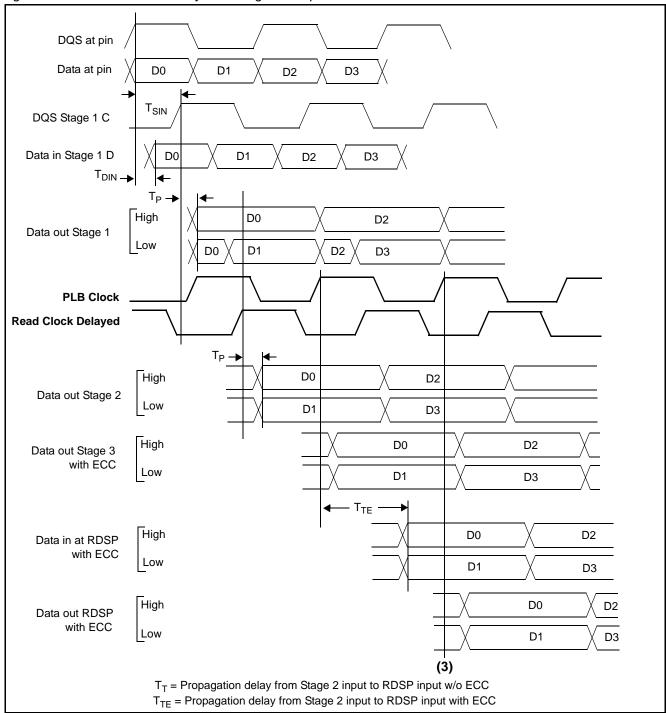

| Figure 14, DDR SDRAM Read Cycle Timing—Example 3        |

## **Tables**

| Table 1. System Memory Address Map                                                           | . 7 |

|----------------------------------------------------------------------------------------------|-----|

| Table 2. DCR Address Map (4KB of Device Configuration Registers)                             | 9   |

| Table 3. Recommended Reflow Soldering Profile                                                | 18  |

| Table 4. JEDEC Moisture Sensitivity Level and Ball Composition                               | 18  |

| Table 5. Signals Listed Alphabetically                                                       | 19  |

| Table 6. Signals Listed by Ball Assignment                                                   | 43  |

| Table 7. Pin Summary                                                                         | 50  |

| Table 8. Signal Functional Description                                                       | 52  |

| Table 9. Absolute Maximum Ratings                                                            | 61  |

| Table 10. Recommended DC Operating Conditions                                                | 61  |

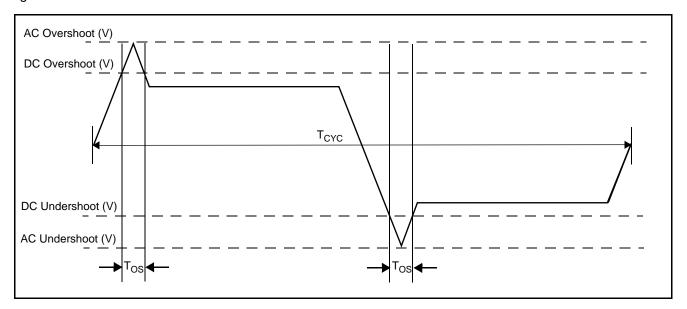

| Table 11. Overshoot and Undershoot                                                           | 63  |

| Table 12. Typical DC Power Supply Requirements                                               |     |

| Table 13. V <sub>DD</sub> Supply Power Dissipation                                           | 65  |

| Table 14. DC Power Supply Current Loads                                                      | 66  |

| Table 15. Package Thermal Specifications                                                     | 67  |

| Table 16. Clocking Specifications                                                            | 68  |

| Table 17. Peripheral Interface Clock Timings                                                 | 70  |

| Table 18. I/O Specifications—PCI, USB, UART, IIC, SPI, Ethernet, System and Debug Interfaces | 72  |

| Table 19. I/O Specifications—EBC, EBMI, DMA and NAND Flash Interfaces                        | 75  |

| Table 20. Input Capacitance                                                                  | 75  |

| Table 21. DDR SDRAM Output Driver Specifications                                             | 78  |

| Table 22. I/O Timing—DDR SDRAM T <sub>DS</sub>                                               | 80  |

| Table 23. I/O Timing—DDR SDRAM T <sub>SK</sub> , T <sub>SA</sub> , and T <sub>HA</sub>       | 80  |

| Table 24. I/O Timing—DDR SDRAM T <sub>SD</sub> and T <sub>HD</sub>                           | 80  |

| Table 25. I/O Timing—DDR SDRAM T <sub>SIN</sub> and T <sub>DIN</sub>                         | 82  |

| Table 26. Stranning Pin Assignments                                                          | 86  |

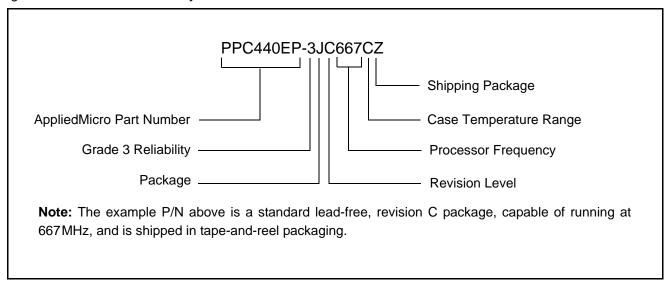

## **Ordering and PVR Information**

For information on the availability of the following parts, contact your local AppliedMicro sales office.

| Product Name | Order Part Number<br>(see Notes:) | Package                | Revision<br>Level | PVR Value  | JTAG ID    |

|--------------|-----------------------------------|------------------------|-------------------|------------|------------|

| PPC440EP     | PPC440EP-3pbfffCx                 | 35mm, 456 ball, E-PBGA | С                 | 0x422218D4 | 0x2A950049 |

#### Notes:

- 1. p = Module Package type

- B = standard (E-PBGA) and contains lead.

- J = standard (E-PBGA) and is lead-free (RoHS compliant)

- 2. b = Chip revision level

- C = Revision level C (2.1)

- 3. fff = Processor frequency

- 333 = 333MHz

- 400 = 400 MHz

- 533 = 533MHz

- 667 = 667MHz

- 4. C = Case temperature range:

- -40°C to + 90°C for 333MHz and 400 MHz parts

- -40°C to +100°C for 533MHz parts

- -40°C to +85°C for 667MHz parts

- 5. x = Shipping package type

- Z = tape-and-reel

Blank = tray

Each part number contains a revision code. This is the die mask revision number and is included in the part number for identification purposes only.

The PVR (Processor Version Register) and the JTAG ID register are software accessible (read-only) and contain information that uniquely identifies the part. Refer to the *PPC440EP User's Manual* for details on accessing these registers.

Figure 1. Order Part Number Key

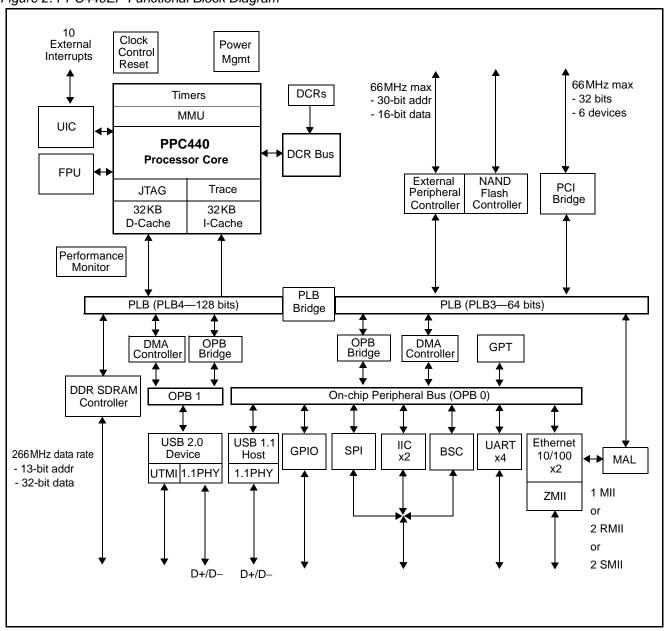

## **Block Diagram**

Figure 2. PPC440EP Functional Block Diagram

The PPC440EP is a system on a chip (SOC).

## **Address Maps**

The PPC440EP incorporates two address maps. The first is a fixed processor System Memory Address Map. This address map defines the possible contents of various address regions which the processor can access. The second is the DCR Address Map for Device Configuration Registers (DCRs). The DCRs are accessed by software running on the PPC440EP processor through the use of **mtdcr** and **mfdcr** instructions.

Table 1. System Memory Address Map (Sheet 1 of 2)

| Function                  | Sub Function                      | Start Address | End Address | Size  |

|---------------------------|-----------------------------------|---------------|-------------|-------|

| Lead Marray 1             | DDR SDRAM                         | 0 0000 0000   | 0 3FFF FFFF | 1GB   |

| Local Memory <sup>1</sup> | Reserved                          | 0 4000 0000   | 0 4FFF FFFF |       |

|                           | OPB Arbiter for USB (OPB 1)       | 0 5000 0000   | 0 5000 003F | 64B   |

| USB 2.0 Device Bus        | Reserved                          | 0 5000 0040   | 0 5000 00FF |       |

| USB 2.0 Device Bus        | USB 2.0 Device                    | 0 5000 0100   | 0 5000 017F | 128B  |

|                           | Reserved                          | 0 5000 0180   | 0 7FFF FFFF |       |

| EBC                       | EBC                               | 0 8000 0000   | 0 9FFF FFFF | 512MB |

|                           | PCI Memory                        | 0 A000 0000   | 0 DFFF FFFF | 1GB   |

|                           | Reserved                          | 0 E000 0000   | 0 E7FF FFFF |       |

|                           | PCI I/O                           | 0 E800 0000   | 0 E800 FFFF | 64KB  |

|                           | Reserved                          | 0 E801 0000   | 0 E87F FFFF |       |

|                           | PCI I/O                           | 0 E880 0000   | 0 EBFF FFFF | 56MB  |

| PCI                       | Reserved                          | 0 EC00 0000   | 0 EEBF FFFF |       |

| FOI                       | Configuration Registers           | 0 EEC0 0000   | 0 EEC0 0007 | 8B    |

|                           | Reserved                          | 0 EEC0 0008   | 0 EECF FFFF |       |

|                           | PCI Interrupt Ack / Special Cycle | 0 EED0 0000   | 0 EED0 0003 | 4B    |

|                           | Reserved                          | 0 EED0 0004   | 0 EF3F FFFF |       |

|                           | Local Configuration Registers     | 0 EF40 0000   | 0 EF40 003F | 64B   |

|                           | Reserved                          | 0 EF40 0040   | 0 EF4F FFFF |       |

Table 1. System Memory Address Map (Sheet 2 of 2)

| Function                        | Sub Function          | Start Address | End Address | Size  |

|---------------------------------|-----------------------|---------------|-------------|-------|

|                                 | Reserved              | 0 EF50 0000   | 0 EF5F FFFF |       |

|                                 | General Purpose Timer | 0 EF60 0000   | 0 EF60 00FF | 256B  |

|                                 | Reserved              | 0 EF60 0100   | 0 EF60 02FF |       |

|                                 | UART0                 | 0 EF60 0300   | 0 EF60 0307 | 8B    |

|                                 | Reserved              | 0 EF60 0308   | 0 EF60 03FF |       |

|                                 | UART1                 | 0 EF60 0400   | 0 EF60 0407 | 8B    |

|                                 | Reserved              | 0 EF60 0408   | 0 EF60 04FF |       |

|                                 | UART2                 | 0 EF60 0500   | 0 EF60 0507 | 8B    |

|                                 | Reserved              | 0 EF60 0508   | 0 EF60 05FF |       |

|                                 | UART3                 | 0 EF60 0600   | 0 EF60 0607 | 8B    |

|                                 | Reserved              | 0 EF60 0608   | 0 EF60 06FF |       |

|                                 | IICO                  | 0 EF60 0700   | 0 EF60 071F | 32B   |

|                                 | Reserved              | 0 EF60 0720   | 0 EF60 07FF |       |

|                                 | IIC1                  | 0 EF60 0800   | 0 EF60 081F | 32B   |

| Internal Peripherals            | Reserved              | 0 EF60 0820   | 0 EF60 08FF |       |

|                                 | SPI                   | 0 EF60 0900   | 0 EF60 0906 | 6B    |

|                                 | Reserved              | 0 EF60 0907   | 0 EF60 09FF |       |

|                                 | OPB Arbiter (OPB 0)   | 0 EF60 0A00   | 0 EF60 0A3F | 64B   |

|                                 | Reserved              | 0 EF60 0A40   | 0 EF60 0AFF |       |

|                                 | GPIO0 Controller      | 0 EF60 0B00   | 0 EF60 0B7F | 128B  |

|                                 | Reserved              | 0 EF60 0B80   | 0 EF60 0BFF |       |

|                                 | GPIO1 Controller      | 0 EF60 0C00   | 0 EF60 0C7F | 128B  |

|                                 | Reserved              | 0 EF60 0C80   | 0 EF60 0CFF |       |

|                                 | Ethernet PHY ZMII     | 0 EF60 0D00   | 0 EF60 0D0F | 16B   |

|                                 | Reserved              | 0 EF60 0D10   | 0 EF60 0DFF |       |

|                                 | Ethernet 0 Controller | 0 EF60 0E00   | 0 EF60 0EFF | 256B  |

|                                 | Ethernet 1 Controller | 0 EF60 0F00   | 0 EF60 0FFF | 256B  |

|                                 | USB 1.1 Host          | 0 EF60 1000   | 0 EF60 107F | 128B  |

|                                 | Reserved              | 0 EF60 1080   | 0 EFFF FFFF |       |

| EBC                             |                       | 0 F000 0000   | 0 FFDF FFFF | 254MB |

| Boot space (EBC Bank 0 and PCI) |                       | 0 FFE0 0000   | 0 FFFF FFFF | 2MB   |

#### Notes

- 1. DDR SDRAM can be located anywhere in the Local Memory area of the memory map.

- 2. EBC and PCI are relocatable, but this map reflects the suggested configuration.

Table 2. DCR Address Map (4KB of Device Configuration Registers)

| Function                             | Start Address | End Address | Size                   |

|--------------------------------------|---------------|-------------|------------------------|

| Total DCR Address Space <sup>1</sup> | 000           | 3FF         | 1KW (4KB) <sup>1</sup> |

| By function:                         |               |             |                        |

| Reserved                             | 000           | 00B         | 12W                    |

| Clocking Power On Reset (CPR)        | 00C           | 00D         | 2W                     |

| System DCRs (SDR)                    | 00E           | 00F         | 2W                     |

| Memory Controller (SDRAM)            | 010           | 011         | 2W                     |

| External Bus Controller (EBC)        | 012           | 013         | 2W                     |

| Reserved                             | 014           | 015         | 2W                     |

| PLB 128 Performance Monitor (PPM)    | 016           | 017         | 2W                     |

| Reserved                             | 018           | 01F         | 8W                     |

| PLB 128 to PLB 64 Bridge Out         | 020           | 02F         | 16W                    |

| PLB 64 to PLB 128 Bridge In          | 030           | 03F         | 16W                    |

| Reserved                             | 040           | 06F         | 64W                    |

| PLB 64 Arbiter                       | 070           | 07F         | 16W                    |

| PLB 128 Arbiter                      | 080           | 08F         | 16W                    |

| PLB 64 to OPB Bridge Out             | 090           | 09F         | 16W                    |

| Reserved                             | 0A0           | 0A7         | 8W                     |

| OPB to PLB 64 Bridge In              | 0A8           | 0AF         | 8W                     |

| Power Management                     | 0B0           | 0B7         | 8W                     |

| Reserved                             | 0B8           | 0BF         | 8W                     |

| Interrupt Controller 0               | 0C0           | 0CF         | 16W                    |

| Interrupt Controller 1               | 0D0           | 0DF         | 16W                    |

| Reserved                             | 0E0           | 0FF         | 32W                    |

| DMA to PLB 64 Controller             | 100           | 13F         | 64W                    |

| Reserved                             | 140           | 17F         | 64W                    |

| Ethernet MAL                         | 180           | 1FF         | 128W                   |

| PLB 128 to OPB Bridge                | 200           | 20F         | 16W                    |

| Reserved                             | 210           | 2FF         | 512W                   |

| DMA to PLB 128 Controller            | 300           | 33F         | 64W                    |

| Reserved                             | 340           | 3FF         | 512W                   |

### Notes:

<sup>1.</sup> DCR address space is addressable with up to 10 bits (1024 or 1K unique addresses). Each unique address represents a single 32-bit (word) register. One kiloword (1024W) equals 4KB (4096 B).

### **PPC440EP Features**

The following sections provide information on the features of the chip.

#### **PowerPC 440 Processor Core**

The PowerPC 440 processor core is designed for high-end applications: RAID controllers, SAN, iSCSI, routers, switches, printers, set-top boxes, etc. It is the first processor core to implement the new Book E PowerPC embedded architecture and the first to use the 128-bit version of IBM's on-chip CoreConnect Bus Architecture.

#### Features include:

- Up to 667MHz operation

- PowerPC Book E architecture

- 32KB I-cache, 32KB D-cache

- UTLB Word Wide parity on data and tag address parity with exception force

- · Three logical regions in D-cache: locked, transient, normal

- · D-cache full line flush capability

- 41-bit virtual address, 36-bit (64GB) physical address

- · Superscalar, out-of-order execution

- · 7-stage pipeline

- 3 execution pipelines

- · Dynamic branch prediction

- · Memory management unit

- 64-entry, full associative, unified TLB with optional parity

- Separate instruction and data micro-TLBs

- Storage attributes for write-through, cache-inhibited, guarded, and big or little endian

- Debug facilities

- Multiple instruction and data range breakpoints

- Data value compare

- Single step, branch, and trap events

- Non-invasive real-time trace interface

- 24 DSP instructions

- Single cycle multiply and multiply-accumulate

- 32 x 32 integer multiply

- 16 x 16 -> 32-bit MAC

### Floating Point Unit (FPU)

### Features include:

- Five stages with 2 MFlops/MHz

- Hardware support for IEEE 754

- Single- and double-precision

- Single-cycle throughput on most instructions

- Thirty-two 64-bit floating point registers

#### **Internal Buses**

The PowerPC 440EP features five standard on-chip buses: two Processor Local Buses (PLBs), two On-Chip Peripheral Buses (OPBs), and the Device Control Register Bus (DCR). The high performance, high bandwidth cores such as the PowerPC 440 processor core, the DDR SDRAM memory controller, and the PCI bridge connect to the PLBs. The primary OPB hosts lower data rate peripherals. The secondary OPB is dedicated to USB 2.0 and DMA. The daisy-chained DCR provides a lower bandwidth path for passing status and control information between the processor core and the other on-chip cores.

#### Features include:

- PLB4

- 128-bit implementation of the PLB architecture

- Separate and simultaneous read and write data paths

- 36-bit address

- Simultaneous control, address, and data phases

- Four levels of pipelining

- Byte-enable capability supporting unaligned transfers

- 32- and 64-byte burst transfers

- 133MHz, maximum 4.25GB/s (simultaneous read and write)

- Processor:bus clock ratios of N:1 and N:2

- PLB3

- 64-bit implementation of the PLB architecture

- 32-bit address

- 133MHz (1:1 ratio with PLB 128), maximum 1.1GB/s (no simultaneous read and write)

- OPB (2)

- 32-bit data path

- 32-bit address

- 66.66MHz

- DCR

- 32-bit data path

- 10-bit address

#### **PCI** Interface

The PCI interface allows connection of PCI devices to the PowerPC processor and local memory. This interface is designed to Version 2.2 of the PCI Specification and supports 32- bit PCI devices.

#### Reference Specifications:

- PowerPC CoreConnect Bus (PLB) Specification Version 3.1

- PCI Specification Version 2.2

- PCI Bus Power Management Interface Specification Version 1.1

#### Features include:

- PCI 2.2

- Frequency to 66MHz

- 32-bit bus

- PCI Host Bus Bridge or an Adapter Device's PCI interface

- Internal PCI arbitration function, supporting up to six external devices, that can be disabled for use with an

external arbiter

- Support for Message Signaled Interrupts

- · Simple message passing capability

- · Asynchronous to the PLB

- PCI Power Management 1.1

- PCI register set addressable both from on-chip processor and PCI device sides

- · Ability to boot from PCI bus memory

- · Error tracking/status

- Supports initiation of transfer to the following address spaces:

- Single beat I/O reads and writes

- Single beat and burst memory reads and writes

- Single beat configuration reads and writes (type 0 and type 1)

- Single beat special cycles

#### **DDR SDRAM Memory Controller**

The Double Data Rate (DDR) SDRAM memory controller supports industry standard discrete devices. Up to four 256MB logical banks are supported in limited configurations. Global memory timings, address and bank sizes, and memory addressing modes are programmable.

#### Features include:

- Registered and non-registered industry standard discrete devices

- 32-bit memory interface with optional 8-bit ECC (SEC/DED)

- Sustainable 1.1 GB/s peak bandwidth at 133 MHz

- SSTL\_2 logic

- 1 to 4 chip selects

- CAS latencies of 2, 2.5 and 3 supported

- DDR200/266 support

- · Page mode accesses (up to eight open pages) with configurable paging policy

- · Programmable address mapping and timing

- Hardware and software initiated self-refresh

- Power management (self-refresh, suspend, sleep)

### **External Peripheral Bus Controller (EBC)**

#### Features include:

- Up to six ROM, EPROM, SRAM, Flash memory, and slave peripheral I/O banks supported

- Up to 66.66MHz operation

- · Burst and non-burst devices

- · 16-bit byte-addressable data bus

- · 30-bit address

- · Peripheral Device pacing with external "Ready"

- · Latch data on Ready, synchronous or asynchronous

- Programmable access timing per device

- 256 Wait States for non-burst

- 32 Burst Wait States for first access and up to 8 Wait States for subsequent accesses

- Programmable CSon, CSoff relative to address

- Programmable OEon, WEon, WEoff (1 to 4 clock cycles) relative to CS

- · Programmable address mapping

- · External DMA Slave Support

- · External master interface

- Write posting from external master

- Read prefetching on PLB for external master reads

- Bursting capable from external master

- Allows external master access to all non-EBC PLB slaves

- External master can control EBC slaves for own access and control

#### **Ethernet Controller Interface**

Ethernet support provided by the PPC440EP interfaces to the physical layer but the PHY is not included on the chip:

- One to two 10/100 interfaces running in full- and half-duplex modes

- One full Media Independent Interface (MII) with 4-bit parallel data transfer

- Two Reduced Media Independent Interfaces (RMII) with 2-bit parallel data transfer

- Two Serial Media Independent Interfaces (SMII)

- Packet reject support

#### **DMA to PLB3 Controller**

This DMA controller provides a DMA interface between the OPB and the 64-bit PLB.

#### Features include:

- Supports the following transfers:

- Memory-to-memory transfers

- Buffered peripheral to memory transfers

- Buffered memory to peripheral transfers

- Four channels

- Scatter/Gather capability for programming multiple DMA operations

- 32-byte buffer

- 8-, 16-, 32-bit peripheral support (OPB and external)

- · 32-bit addressing

- · Address increment or decrement

- Supports internal and external peripherals

- Support for memory mapped peripherals

- Support for peripherals running on slower frequency buses

#### **DMA to PLB4 Controller**

This DMA controller provides a DMA interface dedicated to the USB 2.0 device ports and the 128-bit PLB.

#### Features include:

- 4 independent channels supporting internal USB 2.0 Device endpoints 1 and 2

- · Support for memory-to-memory, peripheral-to-memory, and memory-to-peripheral transfers

- · Scatter/gather capability

- 128-byte buffer with programmable thresholds

### Serial Ports (UART)

#### Features include:

- Up to four ports in the following combinations:

- One 8-pin

- Two 4-pin

- One 4-pin and two 2-pin

- Four 2-pin

- Selectable internal or external serial clock to allow wide range of baud rates

- Register compatibility with NS16550 register set

- · Complete status reporting capability

- · Fully programmable serial-interface characteristics

- · Supports DMA using internal DMA function on PLB 64

#### **IIC Bus Interface**

#### Features include:

- Two IIC interfaces provided

- Support for Philips® Semiconductors I<sup>2</sup>C Specification, dated 1995

- · Operation at 100kHz or 400kHz

- 8-bit data

- 10- or 7-bit address

- · Slave transmitter and receiver

- · Master transmitter and receiver

- · Multiple bus masters

- Two independent 4 x 1 byte data buffers

- · Twelve memory-mapped, fully programmable configuration registers

- One programmable interrupt request signal

- · Provides full management of all IIC bus protocols

- Programmable error recovery

- Includes an integrated boot-strap controller (BSC) that is multiplexed with the IIC0 interface

### Serial Peripheral Interface (SPI/SCP)

The Serial Peripheral Interface (also known as the Serial Communications Port) is a full-duplex, synchronous, character-oriented (byte) port that allows the exchange of data with other serial devices. The SCP is a master on the serial port supporting a 3-wire interface (receive, transmit, and clock), and is a slave on the OPB.

#### Features include:

- · Three-wire serial port interface

- Full-duplex synchronous operation

- · SCP bus master

- · OPB bus slave

- · Programmable clock rate divider

- Clock inversion

- Reverse data

- · Local data loop back for test

### Universal Serial Bus (USB)

The USB interfaces provide both device and host support for version 1.1 and device support for version 2.0. Support for the USB 2.0 Transceiver Macrocell Interface (UTMI) specification is included.

#### Features include:

- USB 1.1 Host port with internal PHY

- USB 2.0 Device UTMI or USB 1.1 Device PHY

- Device support provides 6 end points (3 in, 3 out)

- 1024B FIFO (double buffering of 512B packets)

- FIFOs are not shared between in and out endpoints

- Endpoints do not support high-bandwidth isochronous transfers

- Two USB 2.0 device end points have DMA dedicated channels (DMA to PLB 128)

### **NAND Flash Controller**

The NAND Flash controller provides a simple interface between the EBC and up to four separate external NAND Flash devices. It provides both direct command, address, and data access to the external device as well as a memory-mapped linear region that generates data accesses. NAND Flash device data appears on the peripheral data bus.

### Features include:

- 1 to 4 banks supported on EBC

- Direct Interfacing to:

- Discrete NAND Flash devices (up to 4 devices)

- SmartMedia Card socket (22-pins)

- · Device sizes:

- 4MB and larger supported for read/write access

- 4MB to 256MB for boot-from-NAND flash (size supported depends on addressing mode)

- (512 + 16)-B or (2K + 64)-B device page sizes supported

- Boot-from-NAND: Execute a linear sequence of boot code out of the first 4KB of block 0

- Support DMA to allow direct, no-processor-intervention block copy from NAND Flash to SDRAM

- ECC provides single-bit error correction and double-bit error detection in each 256B of stored data

- Chip selects shared with EBC

### **General Purpose Timers (GPT)**

Provides a separate time base counter and additional system timers in addition to those defined in the processor core.

#### Features include:

- 32-bit Time Base Counter driven by the OPB bus clock

- · Seven 32-bit compare timers

### General Purpose IO (GPIO) Controller

- Controller functions and GPIO registers are programmed and accessed via memory-mapped OPB bus master accesses.

- 64 GPIOs are multiplexed with other functions. DCRs control whether a particular pin that has GPIO capabilities acts as a GPIO or is used for another purpose.

- Each GPIO output is separately programmable to emulate an open drain driver (that is, drives to zero, tri-stated if output bit is 1).

#### **Universal Interrupt Controller (UIC)**

Two Universal Interrupt Controllers (UIC) are employed. They provide control, status, and communications necessary between the external and internal sources of interrupts and the on-chip PowerPC processor.

Note: Processor specific interrupts (for example, page faults) do not use UIC resources.

#### Features include:

- 10 external interrupts

- · Edge triggered or level-sensitive

- · Positive or negative active

- · Non-critical or critical interrupt to the on-chip processor core

- · Programmable interrupt priority ordering

- Programmable critical interrupt vector for faster vector processing

#### **JTAG**

#### Features include:

- IEEE 1149.1 Test Access Port

- IBM RISCWatch Debugger support

- JTAG Boundary Scan Description Language (BSDL)

## **Package Diagram**

Figure 3. 35mm, 456-Ball E-PBGA

## **Assembly Recommendations**

Table 3. Recommended Reflow Soldering Profile

| Profile Feature                                                    | Sn-Pb Eutectic Assembly          | Pb Free Reflow Assembly          |

|--------------------------------------------------------------------|----------------------------------|----------------------------------|

| Average ramp-up rate                                               | 3°C/second max                   | 3°C/second max                   |

| Preheat  - Temperature Min  - Temperature Max  - Time (min to max) | 100°C<br>150°C<br>60-120 Seconds | 150°C<br>180°C<br>60-120 Seconds |

| Time Maintained Above:  - Temperature  - Time                      | 183°C<br>60-150 Seconds          | 230°C<br>30-50 Seconds           |

| Peak Temperature                                                   | 225 +0/-5°C                      | 260 +5/-0°C                      |

| Time within 5°C of Actual Peak Temperature                         | 10-30 Seconds                    | 10-20 Seconds                    |

| Ramp-down Rate                                                     | 6°C/Second Max                   | 6°C/Second Max                   |

| Time 25°C to Peak Temperature                                      | 6 Minutes Max                    | 8 Minutes Max                    |

Table 4. JEDEC Moisture Sensitivity Level and Ball Composition

|                        | Sn-Pb Eutectic Assembly | Pb Free Reflow Assembly |

|------------------------|-------------------------|-------------------------|

| MSL Level              | 3                       | 3                       |

| Solder Ball Metallurgy | 63Sn/37Pb               | Sn/4Ag/05Cu             |

## **Signal Lists**

The following table lists all the external signals in alphabetical order and shows the ball (pin) number on which the signal appears. Multiplexed signals are shown with the default signal (following reset) *not* in brackets and alternate signals in brackets. Multiplexed signals appear alphabetically multiple times in the list—once for each signal name on the ball. The page number listed gives the page in "Signal Functional Description" on page 52 where the signals in the indicated interface group begin. In cases where signals in the same interface group (for example, Ethernet) have different names to distinguish variations in the mode of operation, the names are separated by a comma with the primary mode name appearing first. These signals are listed only once, and appear alphabetically by the primary mode name.

### **Alphabetical Signal List**

Table 5. Signals Listed Alphabetically (Sheet 1 of 24)

| Signal Name                 | Ball | Interface Group            | Page |

|-----------------------------|------|----------------------------|------|

| AGND                        | AE17 | Power                      | 60   |

| $AV_{DD}$                   | AD17 | - Power                    | 60   |

| BA0                         | AF03 | DDD ODDAM                  | 50   |

| BA1                         | AF04 | DDR SDRAM                  | 53   |

| BankSel0                    | R04  |                            |      |

| BankSel1                    | R02  | DDD CDDAM                  | 50   |

| BankSel2                    | R01  | DDR SDRAM                  | 53   |

| BankSel3                    | N01  | 1                          |      |

| [BusReq][USB2TermSel]GPIO31 | AA23 | External Master Peripheral | 56   |

| CAS                         | J02  | DDR SDRAM                  | 53   |

| ClkEn                       | AF05 | DDR SDRAM                  | 53   |

| DM0                         | AE05 |                            |      |

| DM1                         | AD07 | ]                          |      |

| DM2                         | J01  | DDR SDRAM                  | 53   |

| DM3                         | L03  | ]                          |      |

| DM8                         | AF07 | ]                          |      |

| [DMAAck0][IRQ8]GPIO47       | D18  |                            |      |

| [DMAAck1][IRQ4]GPIO44       | G25  | External Slave Peripheral  | 55   |

| [DMAAck2][PerAddr06]GPIO01  | B06  | External Slave Peripheral  | 55   |

| [DMAAck3][PerAddr03]GPIO04  | C07  | 1                          |      |

| [DMAReq0][IRQ7]GPIO46       | B24  |                            |      |

| DMAReq1[IRQ5][ModeCtrl]     | AC12 | Futernal Claus Barisharal  | 55   |

| [DMAReq2][PerAddr07]GPIO00  | C08  | External Slave Peripheral  |      |

| [DMAReq3][PerAddr04]GPIO03  | D08  |                            |      |

Table 5. Signals Listed Alphabetically (Sheet 2 of 24)

| Signal Name                         | Ball | Interface Group            | Page |

|-------------------------------------|------|----------------------------|------|

| DQS0                                | AD09 |                            |      |

| DQS1                                | AC08 |                            |      |

| DQS2                                | K03  | DDR SDRAM                  | 53   |

| DQS3                                | M04  |                            |      |

| DQS8                                | AC06 |                            |      |

| [DrvrInh1]USB2LS0[RejectPkt]        | Y25  | System                     | 59   |

| [DrvrInh2]Halt                      | C25  | - System                   | 59   |

| ECC0                                | P02  |                            |      |

| ECC1                                | N02  |                            |      |

| ECC2                                | M01  |                            |      |

| ECC3                                | M02  | DDR SDRAM                  | 53   |

| ECC4                                | N03  | - DDR SDRAWI               | 55   |

| ECC5                                | N04  |                            |      |

| ECC6                                | L02  |                            |      |

| ECC7                                | M03  |                            |      |

| [EMCCD, EMC1RxErr]GPIO25[NFRdyBusy] | AC16 |                            |      |

| [EMCCrS, EMC0CrsDV]GPIO22           | AD15 |                            |      |

| [EMCDV, EMC1CrsDV]GPIO21[NFREn]     | AF17 |                            |      |

| EMCMDCIk                            | AE16 |                            |      |

| EMCMDIO                             | AC18 |                            |      |

| EMCRxClk                            | AF19 |                            |      |

| [EMCRxD0, EMC0RxD0, EMC0RxD]GPIO12  | AD19 |                            |      |

| [EMCRxD1, EMC0RxD1, EMC1RxD]GPIO13  | AE20 |                            |      |

| [EMCRxD2, EMC1RxD0]GPIO14           | AD18 | Ethornot                   | 54   |

| [EMCRxD3, EMC1RxD1]GPIO15           | AC17 | - Ethernet                 | 54   |

| [EMCRxErr, EMC0RxErr]GPIO20         | AD16 |                            |      |

| EMCTxClk, EMCRefClk                 | AC15 |                            |      |

| [EMCTxD0, EMC0TxD0, EMC0TxD]GPIO16  | AD14 |                            |      |

| [EMCTxD1, EMC0TxD1, EMC1TxD]GPIO17  | AF13 |                            |      |

| [EMCTxD2, EMC1TxD0]GPIO18[NFCLE]    | AF14 |                            |      |

| [EMCTxD3, EMC1TxD1]GPIO19[NFALE]    | AC14 |                            |      |

| [EMCTxEn, EMC0TxEn, EMCSync]GPIO24  | AF20 | 1                          |      |

| [EMCTxErr, EMC1TxEn]GPIO23[NFWEn]   | AF18 | 1                          |      |

| [EOT0/TC0][IRQ9]GPIO48              | A19  |                            |      |

| [EOT1/TC1][IRQ6]GPIO45              | H23  | F. tarvel Olivia Pari i    |      |

| [EOT2/TC2][PerAddr05]GPIO02         | A05  | External Slave Peripheral  | 55   |

| [EOT3/TC3][PerAddr02]GPIO05         | B04  | 1                          |      |

| [ExtAck][USB2XcvrSel]GPIO30         | AA25 | External Master Peripheral | 56   |

| [ExtReq][USB2RxErr]GPIO27           | AD26 | External Master Peripheral | 56   |

Table 5. Signals Listed Alphabetically (Sheet 3 of 24)

| Signal Name | Ball | Interface Group            | Page |

|-------------|------|----------------------------|------|

| ExtReset    | B23  | External Master Peripheral | 56   |

| GND         | A01  |                            |      |

| GND         | A02  |                            |      |

| GND         | A06  |                            |      |

| GND         | A09  | _                          |      |

| GND         | A11  | _                          |      |

| GND         | A16  | 1                          |      |

| GND         | A21  | 7                          |      |

| GND         | A26  | _                          |      |

| GND         | B02  | 7                          |      |

| GND         | B25  | 1                          |      |

| GND         | B26  | 7                          |      |

| GND         | C03  | 7                          |      |

| GND         | C24  | 7                          |      |

| GND         | D04  | 7                          |      |

| GND         | D21  | 1                          |      |

| GND         | D23  | 1                          |      |

| GND         | E09  | Power                      | 60   |

| GND         | E14  |                            |      |

| GND         | E18  | 1                          |      |

| GND         | F01  | 7                          |      |

| GND         | F26  | 7                          |      |

| GND         | J05  |                            |      |

| GND         | J22  |                            |      |

| GND         | J26  |                            |      |

| GND         | L01  |                            |      |

| GND         | L04  |                            |      |

| GND         | L11  | 1                          |      |

| GND         | L13  | 1                          |      |

| GND         | L14  | 1                          |      |

| GND         | L16  | 1                          |      |

| GND         | L26  | 1                          |      |

| GND         | M12  | 1                          |      |

| GND         | M13  | 1                          |      |

Table 5. Signals Listed Alphabetically (Sheet 4 of 24)

| Signal Name | Ball | Interface Group | Page |

|-------------|------|-----------------|------|

| GND         | M15  |                 |      |

| GND         | M25  |                 |      |

| GND         | N05  |                 |      |

| GND         | N11  |                 |      |

| GND         | N13  |                 |      |

| GND         | N14  |                 |      |

| GND         | N15  |                 |      |

| GND         | N16  |                 |      |

| GND         | P11  |                 |      |

| GND         | P12  |                 |      |

| GND         | P13  |                 |      |

| GND         | P14  |                 |      |

| GND         | P16  |                 |      |

| GND         | P22  |                 |      |

| GND         | R12  |                 |      |

| GND         | R14  |                 |      |

| GND         | R15  |                 |      |

| GND         | T01  | Power           | 60   |

| GND         | T11  |                 |      |

| GND         | T13  |                 |      |

| GND         | T14  |                 |      |

| GND         | T16  |                 |      |

| GND         | T26  |                 |      |

| GND         | V05  |                 |      |

| GND         | V01  |                 |      |

| GND         | V22  |                 |      |

| GND         | AA01 |                 |      |

| GND         | AA26 |                 |      |

| GND         | AB09 |                 |      |

| GND         | AB13 |                 |      |

| GND         | AB18 |                 |      |

| GND         | AC01 |                 |      |

| GND         | AC04 |                 |      |

| GND         | AC07 |                 |      |

| GND         | AC23 |                 |      |

Table 5. Signals Listed Alphabetically (Sheet 5 of 24)

| Signal Name | Ball | Interface Group | Page |

|-------------|------|-----------------|------|

| GND         | AD03 |                 |      |

| GND         | AD24 |                 |      |

| GND         | AE01 |                 |      |

| GND         | AE02 |                 |      |

| GND         | AE25 |                 |      |

| GND         | AF01 | - Power         | 60   |

| GND         | AF06 | rowei           | 00   |

| GND         | AF11 |                 |      |

| GND         | AF16 |                 |      |

| GND         | AF21 |                 |      |

| GND         | AF25 |                 |      |

| GND         | AF26 |                 |      |

Table 5. Signals Listed Alphabetically (Sheet 6 of 24)

| Signal Name                         | Ball | Interface Group | Page |

|-------------------------------------|------|-----------------|------|

| GPIO00[PerAddr07][DMAReq2]          | C08  |                 |      |

| GPIO01[PerAddr06][DMAAck2]          | B06  |                 |      |

| GPIO02[PerAddr05][EOT2/TC2]         | A05  |                 |      |

| GPIO03[PerAddr04][DMAReq3]          | D08  |                 |      |

| GPIO04[PerAddr03][DMAAck3]          | C07  |                 |      |

| GPIO05[PerAddr02][EOT3/TC3]         | B04  |                 |      |

| GPIO06[PerCS1][NFCE1]               | C06  |                 |      |

| GPIO07[PerCS2][NFCE2]               | A04  |                 |      |

| GPIO08[PerCS3][NFCE3]               | B07  |                 |      |

| GPIO09[PerCS4]                      | B10  |                 |      |

| GPIO10[PerCS5]                      | A10  |                 |      |

| GPIO11[PerErr]                      | E04  |                 |      |

| GPIO12[EMCRxD0, EMC0RxD0, EMC0RxD]  | AD19 |                 |      |

| GPIO13[EMCRxD1, EMC0RxD1, EMC1RxD]  | AE20 |                 |      |

| GPIO14[EMCRxD2, EMC1RxD0]           | AD18 |                 |      |

| GPIO15[EMCRxD3, EMC1RxD1]           | AC17 | Sustan          | 50   |

| GPIO16[EMCTxD0, EMC0TxD0, EMC0TxD]  | AD14 | System          | 59   |

| GPIO17[EMCTxD1, EMC0TxD1, EMC1TxD]  | AF13 |                 |      |

| GPIO18[EMCTxD2, EMC1TxD0][NFCLE]    | AF14 |                 |      |

| GPIO19[EMCTxD3, EMC1TxD1][NFALE]    | AC14 |                 |      |

| GPIO20[EMCRxErr, EMC0RxErr]         | AD16 |                 |      |

| GPIO21[EMCDV, EMC1CrsDV][NFREn]     | AF17 |                 |      |

| GPIO22[EMCCrS, EMC0CrsDV]           | AD15 |                 |      |

| GPIO23[EMCTxErr, EMC1TxEn][NFWEn]   | AF18 |                 |      |

| GPIO24[EMCTxEn, EMC0TxEn, EMCSync]  | AF20 |                 |      |

| GPIO25[EMCCD, EMC1RxErr][NFRdyBusy] | AC16 | -               |      |

| GPIO26[USB2RxDV]                    | AC26 |                 |      |

| GPIO27[USB2RxErr][ExtReq]           | AD26 |                 |      |

| GPIO28[USB2TxVal]                   | Y24  |                 |      |

| GPIO29[USB2Susp][HoldAck]           | AB25 |                 |      |

| GPIO30[USB2XcvrSel][ExtAck]         | AA25 |                 |      |

| GPIO31[USB2TermSel][BusReq]         | AA23 |                 |      |

Table 5. Signals Listed Alphabetically (Sheet 7 of 24)

| Signal Name                          | Ball | Interface Group            | Page |

|--------------------------------------|------|----------------------------|------|

| GPIO32[USB2OM0]                      | W24  |                            |      |

| GPIO33[USB2OM1]                      | AB26 |                            |      |

| GPIO34[UART0_DCD/UART1_CTS/UART2_Tx] | R25  |                            |      |

| GPIO35[UART0_DSR/UART1_RTS/UART2_Rx] | U26  |                            |      |

| GPIO36[UART0_CTS/UART3_Rx]           | V26  |                            |      |

| GPIO37[UART0_RTS/UART3_Tx]           | R26  |                            |      |

| GPIO38[UART0_DTR/UART1_Tx]           | N24  |                            |      |

| GPIO39[UART0_RI/UART1_Rx]            | P24  |                            |      |

| GPIO40[IRQ0]                         | D03  |                            |      |

| GPIO41[IRQ1]                         | G04  |                            |      |

| GPIO42[IRQ2]                         | F02  |                            |      |

| GPIO43[IRQ3]                         | G02  |                            |      |

| GPIO44[IRQ4][DMAAck1]                | G25  |                            |      |

| GPIO45[IRQ6][EOT1/TC1]               | H23  |                            |      |

| GPIO46[IRQ7][DMAReq0]                | B24  |                            |      |

| GPIO47[IRQ8][DMAAck0]                | D18  | 0                          | 59   |

| GPIO48[IRQ9][EOT0/TC0]               | A19  | System                     |      |

| GPIO49[TrcBS0]                       | AE21 |                            |      |

| GPIO50[TrcBS1]                       | AC25 |                            |      |

| GPIO51[TrcBS2]                       | AA24 |                            |      |

| GPIO52[TrcES0]                       | Y03  |                            |      |

| GPIO53[TrcES1]                       | AA04 |                            |      |

| GPIO54[TrcES2]                       | AB03 |                            |      |

| GPIO55[TrcES3]                       | AB04 |                            |      |

| GPIO56[TrcES4]                       | AF22 |                            |      |

| GPIO57[TrcTS0]                       | AC22 |                            |      |

| GPIO58[TrcTS1]                       | AE24 |                            |      |

| GPIO59[TrcTS2]                       | AD04 |                            |      |

| GPIO60[TrcTS3]                       | AD06 |                            |      |

| GPIO61[TrcTS4]                       | AC09 | 1                          |      |

| GPIO62[TrcTS5]                       | AD12 | 1                          |      |

| GPIO63[TrcTS6]                       | AE15 | 1                          |      |

| Halt[DrvrInh2]                       | C25  | System                     | 59   |

| [HoldAck][USB2Susp]GPIO29            | AB25 |                            |      |

| [HoldPri]USB2LS1[LeakTest]           | V24  | External Master Peripheral | 56   |

| [HoldReq]USB2RxAct[RcvrInh]          | Y23  | 1                          |      |

| IICOSCIk                             | U25  | IICO Porinharal            | 50   |

| IIC0SData                            | T24  | - IIC0 Peripheral          | 56   |

Table 5. Signals Listed Alphabetically (Sheet 8 of 24)

| Signal Name                | Ball | Interface Group | Page |

|----------------------------|------|-----------------|------|

| [IIC1SClk]SCPClkOut        | U24  | IIC1 Peripheral | 56   |

| [IIC1SData]SCPDI           | V25  | not reliptietal | 36   |

| [IRQ0]GPIO40               | D03  |                 |      |

| [IRQ1]GPIO41               | G04  |                 |      |

| [IRQ2]GPIO42               | F02  |                 |      |

| [IRQ3]GPIO43               | G02  |                 |      |

| [IRQ4]GPIO44[DMAAck1]      | G25  | latana inta     | 50   |

| [IRQ5][ModeCtrl]DMAReq1    | AC12 | Interrupts      | 58   |

| [IRQ6]GPIO45[EOT1/TC1]     | H23  |                 |      |

| [IRQ7]GPIO46[DMAReq0]      | B24  |                 |      |

| [IRQ8]GPIO47[DMAAck0]      | D18  |                 |      |

| [IRQ9]GPIO48[EOT0/TC0]     | A19  |                 |      |

| [LeakTest]USB2LS1[HoldPri] | V24  | System          | 59   |

| MemAddr00                  | P01  |                 |      |

| MemAddr01                  | P04  |                 |      |

| MemAddr02                  | T02  |                 |      |

| MemAddr03                  | T04  |                 |      |

| MemAddr04                  | U01  |                 |      |

| MemAddr05                  | V02  |                 |      |

| MemAddr06                  | U04  | DDR SDRAM       | 53   |

| MemAddr07                  | W03  |                 |      |

| MemAddr08                  | Y02  |                 |      |

| MemAddr09                  | AB02 |                 |      |

| MemAddr10                  | R03  |                 |      |

| MemAddr11                  | AD01 |                 |      |

| MemAddr12                  | AD02 |                 |      |

| MemClkOut0                 | AF12 | DDD CDDAM       | 52   |

| MemClkOut0                 | AE13 | DDR SDRAM       | 53   |

Table 5. Signals Listed Alphabetically (Sheet 9 of 24)

| Signal Name             | Ball | Interface Group | Page |

|-------------------------|------|-----------------|------|

| MemData00               | AE12 |                 |      |

| MemData01               | AD13 |                 |      |

| MemData02               | AC13 |                 |      |

| MemData03               | AE11 |                 |      |

| MemData04               | AF10 |                 |      |

| MemData05               | AE10 |                 |      |

| MemData06               | AC11 |                 |      |

| MemData07               | AF09 |                 |      |

| MemData08               | AE09 |                 |      |

| MemData09               | AD10 |                 |      |

| MemData10               | AF08 |                 |      |

| MemData11               | AE08 |                 |      |

| MemData12               | AC10 |                 |      |

| MemData13               | AE07 |                 |      |

| MemData14               | AD08 |                 |      |

| MemData15               | AD05 | DDR SDRAM       | 53   |

| MemData16               | AE03 | DDK ODKAWI      | 33   |

| MemData17               | AC05 |                 |      |

| MemData18               | AF02 |                 |      |

| MemData19               | AC03 |                 |      |

| MemData20               | AC02 |                 |      |

| MemData21               | AA03 |                 |      |

| MemData22               | Y04  |                 |      |

| MemData23               | AA02 |                 |      |

| MemData24               | V04  |                 |      |

| MemData25               | Y01  |                 |      |

| MemData26               | V03  |                 |      |

| MemData27               | W02  |                 |      |

| MemData28               | W01  |                 |      |

| MemData29               | U03  |                 |      |

| MemData30               | T03  |                 |      |

| MemData31               | U02  |                 |      |

| MemSelfRef              | AE04 | DDR SDRAM       | 53   |

| [ModeCtrl][IRQ5]DMAReq1 | AC12 | System          | 59   |

Table 5. Signals Listed Alphabetically (Sheet 10 of 24)

| Signal Name                         | Ball | Interface Group                              | Page |

|-------------------------------------|------|----------------------------------------------|------|

| [NFALE][EMCTxD3, EMC1TxD1]GPIO19    | AC14 |                                              |      |

| [NFCE0]PerCS0                       | D06  |                                              |      |

| [NFCE1][PerCS1]GPIO06               | C06  | ]                                            |      |

| [NFCE2][PerCS2]GPIO07               | A04  |                                              |      |

| [NFCE3][PerCS3]GPIO08               | B07  | NAND Flash                                   | 58   |

| [NFCLE][EMCTxD2, EMC1TxD0]GPIO18    | AF14 | ]                                            |      |

| [NFRdyBusy][EMCCD, EMC1RxErr]GPIO25 | AC16 |                                              |      |

| [NFREn][EMCDV, EMC1CrsDV]GPIO21     | AF17 | ]                                            |      |

| [NFWEn][EMCTxErr, EMC1TxEn]GPIO23   | AF18 |                                              |      |

| No ball                             | F06  |                                              |      |

| No ball                             | F07  | 1                                            |      |

| No ball                             | F08  | 1                                            |      |

| No ball                             | F09  | ]                                            |      |

| No ball                             | F10  | 1                                            |      |

| No ball                             | F11  |                                              |      |

| No ball                             | F12  |                                              |      |

| No ball                             | F13  |                                              |      |

| No ball                             | F14  |                                              |      |

| No ball                             | F15  |                                              |      |

| No ball                             | F16  |                                              |      |

| No ball                             | F17  |                                              |      |

| No ball                             | F18  | A physical ball does not exist at these ball |      |

| No ball                             | F19  | coordinates.                                 | NA   |

| No ball                             | F20  |                                              |      |

| No ball                             | F21  |                                              |      |

| No ball                             | G06  |                                              |      |

| No ball                             | G07  |                                              |      |

| No ball                             | G08  | ]                                            |      |

| No ball                             | G09  | ]                                            |      |

| No ball                             | G10  | ]                                            |      |

| No ball                             | G11  | ]                                            |      |

| No ball                             | G12  | 1                                            |      |

| No ball                             | G13  | ]                                            |      |

| No ball                             | G14  | ]                                            |      |

| No ball                             | G15  | ]                                            |      |

Table 5. Signals Listed Alphabetically (Sheet 11 of 24)

| Signal Name | Ball | Interface Group                              | Page |

|-------------|------|----------------------------------------------|------|

| No ball     | G16  |                                              |      |

| No ball     | G17  |                                              |      |

| No ball     | G18  |                                              |      |

| No ball     | G19  |                                              |      |

| No ball     | G20  |                                              |      |

| No ball     | G21  |                                              |      |

| No ball     | H06  |                                              |      |

| No ball     | H07  |                                              |      |

| No ball     | H08  |                                              |      |

| No ball     | H09  |                                              |      |

| No ball     | H10  |                                              |      |

| No ball     | H11  |                                              |      |

| No ball     | H12  |                                              | NA   |

| No ball     | H13  |                                              |      |

| No ball     | H14  |                                              |      |

| No ball     | H15  |                                              |      |

| No ball     | H16  |                                              |      |

| No ball     | H17  | A physical ball does not exist at these ball |      |

| No ball     | H18  | coordinates.                                 |      |

| No ball     | H19  |                                              |      |

| No ball     | H20  |                                              |      |

| No ball     | H21  |                                              |      |

| No ball     | J06  |                                              |      |

| No ball     | J07  |                                              |      |

| No ball     | J08  |                                              |      |

| No ball     | J09  |                                              |      |

| No ball     | J10  |                                              |      |

| No ball     | J11  |                                              |      |

| No ball     | J12  | -<br>-<br>-<br>-                             |      |

| No ball     | J13  |                                              |      |

| No ball     | J14  |                                              |      |

| No ball     | J15  |                                              |      |

| No ball     | J16  |                                              |      |

| No ball     | J17  |                                              |      |

| No ball     | J18  |                                              |      |

| No ball     | J19  |                                              |      |

Table 5. Signals Listed Alphabetically (Sheet 12 of 24)

| Signal Name | Ball | Interface Group                                           | Page |

|-------------|------|-----------------------------------------------------------|------|

| No ball     | J20  |                                                           |      |

| No ball     | J21  |                                                           |      |

| No ball     | K06  |                                                           |      |

| No ball     | K07  |                                                           |      |

| No ball     | K08  |                                                           |      |

| No ball     | K09  |                                                           |      |

| No ball     | K10  |                                                           |      |

| No ball     | K11  |                                                           |      |

| No ball     | K12  |                                                           |      |

| No ball     | K13  |                                                           |      |

| No ball     | K14  |                                                           |      |

| No ball     | K15  |                                                           |      |

| No ball     | K16  |                                                           |      |

| No ball     | K17  |                                                           | NA   |

| No ball     | K18  |                                                           |      |

| No ball     | K19  |                                                           |      |

| No ball     | K20  |                                                           |      |

| No ball     | K21  | A physical ball does not exist at these ball coordinates. |      |

| No ball     | L06  |                                                           |      |

| No ball     | L07  |                                                           |      |

| No ball     | L08  |                                                           |      |

| No ball     | L09  |                                                           |      |

| No ball     | L10  |                                                           |      |

| No ball     | L17  |                                                           |      |

| No ball     | L18  |                                                           |      |

| No ball     | L19  |                                                           |      |

| No ball     | L20  |                                                           |      |

| No ball     | L21  |                                                           |      |

| No ball     | M06  |                                                           |      |

| No ball     | M07  |                                                           |      |

| No ball     | M08  |                                                           |      |

| No ball     | M09  |                                                           |      |

| No ball     | M10  |                                                           |      |

| No ball     | M17  |                                                           |      |

| No ball     | M18  |                                                           |      |

Table 5. Signals Listed Alphabetically (Sheet 13 of 24)

| Signal Name | Ball | Interface Group                              | Page |

|-------------|------|----------------------------------------------|------|

| No ball     | M19  |                                              |      |

| No ball     | M20  |                                              |      |

| No ball     | M21  |                                              |      |

| No ball     | N06  |                                              |      |

| No ball     | N07  |                                              |      |

| No ball     | N08  |                                              |      |

| No ball     | N09  |                                              |      |

| No ball     | N10  |                                              |      |

| No ball     | N17  |                                              |      |

| No ball     | N18  |                                              |      |

| No ball     | N19  |                                              |      |

| No ball     | N20  |                                              |      |

| No ball     | N21  |                                              |      |

| No ball     | P06  |                                              |      |

| No ball     | P07  |                                              |      |

| No ball     | P08  |                                              |      |

| No ball     | P09  |                                              |      |

| No ball     | P10  | A physical ball does not exist at these ball | NA   |

| No ball     | P17  | coordinates.                                 | INA  |

| No ball     | P18  |                                              |      |

| No ball     | P19  |                                              |      |

| No ball     | P20  |                                              |      |

| No ball     | P21  |                                              |      |

| No ball     | R06  |                                              |      |

| No ball     | R07  |                                              |      |

| No ball     | R08  |                                              |      |

| No ball     | R09  |                                              |      |

| No ball     | R10  |                                              |      |

| No ball     | R17  |                                              |      |

| No ball     | R18  |                                              |      |

| No ball     | R19  |                                              |      |

| No ball     | R20  |                                              |      |

| No ball     | R21  |                                              |      |

| No ball     | T06  |                                              |      |

| No ball     | T07  |                                              |      |

| No ball     | T08  |                                              |      |

Table 5. Signals Listed Alphabetically (Sheet 14 of 24)

| Signal Name | Ball | Interface Group                                           | Page |

|-------------|------|-----------------------------------------------------------|------|

| No ball     | T09  |                                                           |      |

| No ball     | T10  |                                                           |      |

| No ball     | T17  |                                                           |      |

| No ball     | T18  |                                                           |      |

| No ball     | T19  |                                                           |      |

| No ball     | T20  |                                                           |      |

| No ball     | T21  |                                                           |      |

| No ball     | U06  |                                                           |      |

| No ball     | U07  |                                                           |      |

| No ball     | U08  |                                                           |      |

| No ball     | U09  |                                                           |      |

| No ball     | U10  |                                                           |      |

| No ball     | U11  |                                                           |      |

| No ball     | U12  |                                                           |      |

| No ball     | U13  |                                                           |      |

| No ball     | U14  |                                                           |      |

| No ball     | U15  |                                                           |      |

| No ball     | U16  | A physical ball does not exist at these ball coordinates. | NA   |

| No ball     | U17  |                                                           |      |

| No ball     | U18  |                                                           |      |

| No ball     | U19  |                                                           |      |

| No ball     | U20  |                                                           |      |

| No ball     | U21  |                                                           |      |

| No ball     | V06  |                                                           |      |

| No ball     | V07  |                                                           |      |

| No ball     | V08  |                                                           |      |

| No ball     | V09  |                                                           |      |

| No ball     | V10  |                                                           |      |

| No ball     | V11  |                                                           |      |

| No ball     | V12  |                                                           |      |

| No ball     | V13  |                                                           |      |

| No ball     | V14  |                                                           |      |

| No ball     | V15  |                                                           |      |

| No ball     | V16  |                                                           |      |

| No ball     | V17  |                                                           |      |

Table 5. Signals Listed Alphabetically (Sheet 15 of 24)

| Signal Name | Ball | Interface Group                              | Page |

|-------------|------|----------------------------------------------|------|

| No ball     | V18  |                                              |      |

| No ball     | V19  |                                              |      |

| No ball     | V20  |                                              |      |

| No ball     | V21  |                                              |      |

| No ball     | W06  |                                              |      |

| No ball     | W07  |                                              |      |

| No ball     | W08  |                                              |      |

| No ball     | W09  |                                              |      |

| No ball     | W10  |                                              |      |

| No ball     | W11  |                                              |      |

| No ball     | W12  |                                              |      |

| No ball     | W13  |                                              |      |

| No ball     | W14  |                                              |      |

| No ball     | W15  |                                              | NA   |

| No ball     | W16  |                                              |      |

| No ball     | W17  |                                              |      |

| No ball     | W18  |                                              |      |

| No ball     | W19  | A physical ball does not exist at these ball |      |

| No ball     | W20  | coordinates.                                 |      |

| No ball     | W21  |                                              |      |

| No ball     | Y06  |                                              |      |

| No ball     | Y07  |                                              |      |

| No ball     | Y08  |                                              |      |

| No ball     | Y09  |                                              |      |

| No ball     | Y10  |                                              |      |

| No ball     | Y11  |                                              |      |

| No ball     | Y12  |                                              |      |

| No ball     | Y13  |                                              |      |

| No ball     | Y14  |                                              |      |

| No ball     | Y15  |                                              |      |

| No ball     | Y16  | -<br>-<br>-                                  |      |

| No ball     | Y17  |                                              |      |

| No ball     | Y18  |                                              |      |

| No ball     | Y19  |                                              |      |

| No ball     | Y20  |                                              |      |

| No ball     | Y21  |                                              |      |

Table 5. Signals Listed Alphabetically (Sheet 16 of 24)

| Signal Name      | Ball | Interface Group                                           | Page |